## **CJC6822A**

# A Cortex-M0+ based MCU, designed for USB Headphone Appliances

#### **Revision History**

| Version | Author | Date       | Note                  |

|---------|--------|------------|-----------------------|

| V1.0    | Loyal  | 2021-07-15 | Draft vision          |

| V1.1    | Loyal  | 2022-02-15 | Mistake               |

| V1.2    | Loyal  | 2022-06-14 | Add Power-on sequence |

www.eshine-ic.com 1 / 92 2022.06

#### 1. Overview

CJC6822 is a Cortex-M0+ based MCU, designed for USB headphone appliances. It integrates one 32-bit RISC CPU with 16KB SRAM, USB, UART, IIC, audio codec, GPIO, TIMER, WDT, PWM, SPI, IIS, SPDIF, SARADC, PLL, LDO etc.

CJC6822 can boot from external flash through SPI interface. After powered on, the program is read from external flash into internal SRAM for execution.

The CJC6822 can run up to 48MHz, and it is designed with special care to minimize the power consumption while allowing for the flexibility to reach for high performance. It includes the clock gating for individual IP, and CJC6822 can be further operated under different power-saving modes: Normal, Idle, Standby, Power-down, different mode have different clock and power strategy.

#### 1.1 Features

- Cortex-M0+ Like

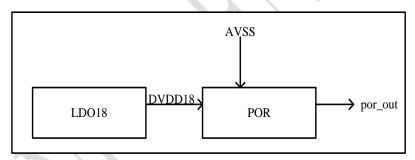

- LDO

- Built-in LDO for wide operating voltage range:3.3V/1.8V

- Memory

- Support program memory up to 16KB

- ◆ RAM:16KB SRAM

- In-system programming & In-Circuit programming by USB/UART

- Clock control

- Programmable system clock source

- ◆ 4-6MHz internal RC-oscillator(1% accuracy at 25°C)

- ◆ 12MHz clock from USB oscillator

- Support external crystal oscillator

- 10KHz internal low-power RC-oscillator for watchdog and idle wake-up

- USB Compliance

- USB Spec.V2.0 high speed/full speed mode compatible

- ◆ USB Audio Class V1.0/V2.0 compatible

- ◆ USB Human Interface Device V1.1 compatible

- Support USB suspend/resume/reset function

- Support control, interrupt, bulk and isochronous data transfer

- Audio codec

- Default sample rate:192K/176.4K/96K/88.2K/48K/44.1K

- ◆ Support bit length:16/20/24/32bit

- I/O port

- ◆ Up to 8 general purpose I/O(GPIO)

- TIMER

- 3 internal timers

- Internal or external clock source selection

www.eshine-ic.com 2 / 92 2022.06

- Interrupt can be issued upon overflow and time-up

- Each timer has two match registers

- Supports the incrementing and decrementing models

- Watchdog Timer

- ◆ During the timeout, the outputs are one or a combination of the following signals

- ----System reset

- ----System interrupt

- ----External interrupt

- ◆ 32-bit down counter

- ◆ Internal or external clock source selection

- A variable time-out period of reset

- Access protection

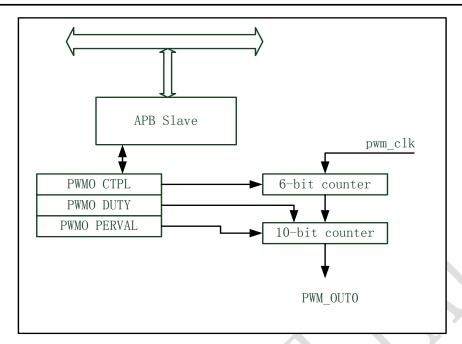

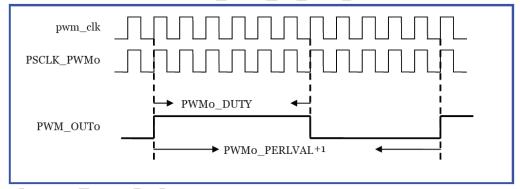

- PWM

- One 16-bit timers PWM channel

- Programmable duty control of output waveform

- Auto reload mode or one-shot pulse mode

- Capture and compare function

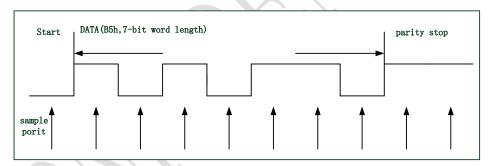

- UART

- Programmable baud rates ,Baud rate up to 921.6K

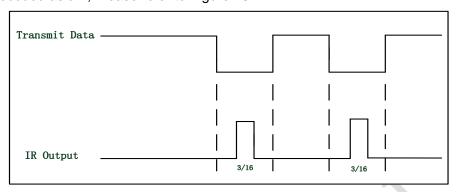

- Support 38KHz house IR transceiver

- SPI

- One specified SPI interface as AHB device for boot loader and APB device for write back

- speed up to 40MHz

- I2C

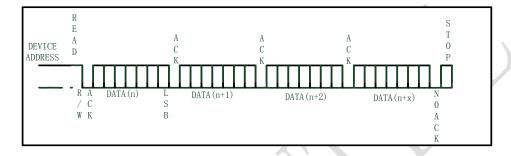

- compatible with Philips IIC standard

- I2S/SPDIF

- ◆ support the Sony/Philips Digital Interface Format(SPDIF) transmitter

- support master/slave mode and 16/24/32bit data width

- SARADC

- 1 channel analog input

- 8bit SARADC, 4bit accuracy is guaranteed

- Brown out reset

- Programmable 3 threshold levels: 2.7V/2.4V/2.0V(default 2.0V)

- Optional BOD interrupt or reset

- Operating temperature:-20~+85 Degree

- Package: QFN48 6\*6

www.eshine-ic.com 3 / 92 2022.06

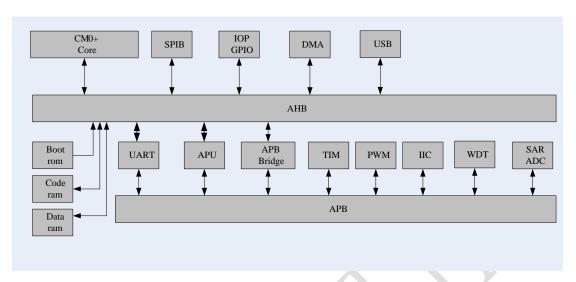

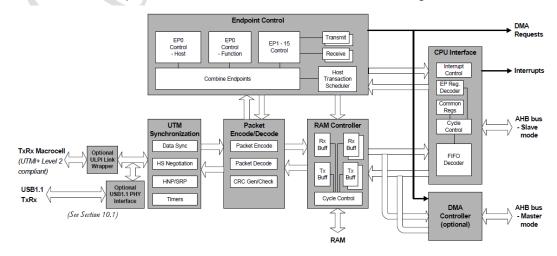

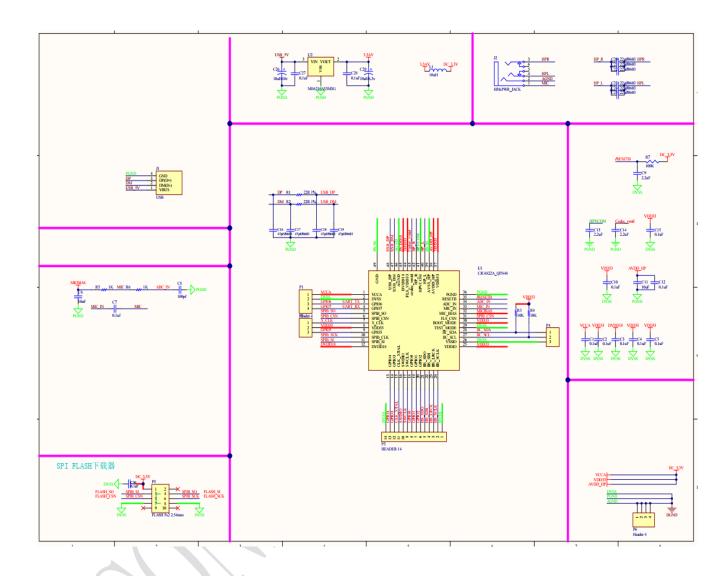

## 1.2 System diagram

Figure 1. CJC6822 chip block diagram

<u>www.eshine-ic.com</u> 4 / 92 2022.06

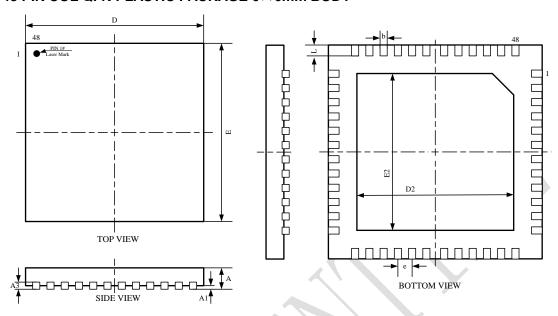

## 2 .PIN diagram

## 2.1 QFN48 PACKAGE

| 48     | 47     | 46    | 45     | 44    | 43         | 42   | 41     | 40   | 39      | 38      | 37    |

|--------|--------|-------|--------|-------|------------|------|--------|------|---------|---------|-------|

| USB_DP | USB_DM | A1GND | DVDD18 | VDD33 | Codec_Vmid | HP_R | HPVCOM | HP_L | AVSS_HP | AVDD_HP | AVDDD |

| 1  | VCCA1     |         |       |           |     |    |       |       |       |         |           |          |          | PGND     | 36 |

|----|-----------|---------|-------|-----------|-----|----|-------|-------|-------|---------|-----------|----------|----------|----------|----|

| 2  | DVSS      |         |       |           |     |    |       |       |       |         |           |          |          | RESETB   | 35 |

| 3  | UART_TX   |         |       |           |     |    |       |       |       |         |           |          |          | ADC_IN   | 34 |

|    | (GPIO6)   |         |       |           |     |    |       |       |       |         |           |          |          | _        |    |

| 4  | UART_RX   |         |       |           |     |    |       |       |       |         |           |          |          | MIC_IN   | 33 |

| 4  | (GPIO7)   |         |       |           |     |    |       |       |       |         |           |          |          | WIIC_IIV | 33 |

| 5  | SPIB_SO   |         |       |           |     |    |       |       |       |         |           |          |          | MICBIAS  | 32 |

| 6  | SPIB_CSN  |         | 49    |           |     |    |       |       |       |         | FLS_CSN   | 31       |          |          |    |

| 7  | XCLK/MCLK | GND/VSS |       |           |     |    |       |       |       | AVDD    | 30        |          |          |          |    |

| 8  | VDD33     |         |       |           |     |    |       |       |       |         | TEST_MODE | 29       |          |          |    |

| 9  | GPIO5     |         |       |           |     |    |       |       |       |         |           |          |          | IIC_SDA  | 28 |

| 10 | SPIB_CLK  |         |       |           | , < |    |       |       |       |         |           |          |          | IIC_SCL  | 27 |

| 11 | SPIB_SI   |         |       |           |     |    |       |       |       |         |           |          |          | VSSIO0   | 26 |

| 12 | DVDD18    |         |       |           |     |    |       |       |       |         |           |          |          | VDDIO1   | 25 |

|    |           | GPI04   | GPI03 | CLK_XTALa | NC  | NC | GPI00 | GPI01 | GPI02 | OGS_SII | IIS_SDI   | IIS_LRCK | IIS_SCLK |          |    |

|    |           | 13      | 14    | 15        | 16  | 17 | 18    | 19    | 20    | 21      | 22        | 23       | 24       |          |    |

<u>www.eshine-ic.com</u> 5 / 92 2022.06

## 3 .PIN description

#### **QFN48 PACKAGE PIN DESCRIPTION**

| 48 Pin No.  | PIN_NAME   | IO_TYPE | COMMENT                        |

|-------------|------------|---------|--------------------------------|

| DIGITAL PIN |            |         |                                |

| 3           | UART_TX    | IO      | UART transmitter(GPIO6)        |

| 4           | UART_RX    | Ю       | UART transmitter(GPIO7)        |

| 5           | SPIB_SO    | Ю       | SPI data out for boot flash    |

| 6           | SPIB_CSN   | Ю       | SPI CSN                        |

| 9           | GPIO5      | Ю       | GPIO5                          |

| 10          | SPIO_CLK   | Ю       | SPI CLOCK for boot flash       |

| 11          | SPIB_SI    | Ю       | SPI data in for boot flash     |

| 13          | GPIO4      | Ю       | GPIO4                          |

| 14          | GPIO3      | Ю       | GPIO3                          |

| 16          | SWDIO      | Ю       | NC                             |

| 17          | SWCLK      | Ю       | NC                             |

| 18          | GPIO0      | Ю       | GPIO0(PWM OUT)                 |

| 19          | GPIO1      | Ю       | GPIO1                          |

| 20          | GPIO2      | Ю       | GPIO2                          |

| 21          | IIS_SDO    | Ю       | IIS DATA OUTPUT                |

| 22          | IIS_SDI    | Ю       | IIS DATA INPUT                 |

| 23          | IIS_LRCK   | 10      | IIS SAMPLING RATE CLOCK IN/OUT |

| 24          | IIS_SCLK   | Ю       | IIS DATA CLOCK IN/OUT          |

| 27          | IIC_SCL    | 10      | IIC DATA CLOCK IN/OUT          |

| 28          | IIC_SDA    | Ю       | IIC DATA IN/OUT                |

| 31          | FLS_CSN    | 10      | SPI CHIP SELECT FOR BOOT FLASH |

| 7           | XCLK/MCLK  | Ю       | IIS MCLK                       |

| 29          | TEST MODE  |         | GND                            |

| 30          | 1111       |         |                                |

| ANALOG PIN  |            |         |                                |

| 48          | USB_DP     | Ю       | USB DP                         |

| 32          | MIC_BIAS   | Ю       | Mic Bias                       |

| 33          | MIC_IN     | Ю       | Mic input                      |

| 34          | ADC_IN     | Ю       | ADC input                      |

| 35          | RESETB     | Ю       | RESET                          |

| 40          | HP_L       | Ю       | left HP                        |

| 41          | HP_VCOM    | Ю       | HP Voltage Reference           |

| 42          | HP_R       | Ю       | right HP                       |

| 43          | Codec_Vmid | Ю       | Codec Voltage Reference        |

| 47          | USB_DM     | Ю       | USB DM                         |

| 48          | USB_DP     | Ю       | USB DP                         |

| POWER       |            |         |                                |

| 1           | VCCA1      | POWER   | Power for USB digital          |

| 2     | DVSS      | GROUND | Ground for Digital           |

|-------|-----------|--------|------------------------------|

| 8     | VDD33     | POWER  | Power for IO                 |

| 12    | DVDD18    | POWER  | Power for Core               |

| 25    | VDDIO1    | POWER  | Power for IO                 |

| 26    | VSSIO0    | GROUND | Ground for IO                |

| 30    | BOOT_MODE | POWER  | Power for Core               |

| 37    | AVDD      | POWER  | Power for HP                 |

| 38    | AVDD_HP   | POWER  | Power for HP                 |

| 39    | AVSS_HP   | POWER  | Ground for HP                |

| 44    | FLS_VDD33 | POWER  | power for Flash              |

| 45    | DVDD18    | POWER  | Power for Core               |

| 46    | A1GND     | GROUND | Ground for USB               |

| 49    | GND/VSS   | GROUND | Ground for Digital           |

| RESET |           |        |                              |

| 36    | GND       | Ю      | Ground for IO                |

| CLK   |           |        |                              |

| 15    | CLK_XTALa | Ю      | 12MHz OSC INPUT( default NC) |

|       |           |        |                              |

|       |           |        |                              |

#### 4 .ELECTRICAL CHARACTERISTICS

**Test Conditions**

AVDD = AVDD\_HP = VDD33 = VCCA2 = VCCA1 = VDD\_IO1 = 3.3V, All module is power on, TA =  $25^{\circ}$ C (unless otherwise noted).

| PARAMETER                 | SYMBOL  | TEST<br>CONDITIONS   | MIN | TYP  | MAX | UNIT |

|---------------------------|---------|----------------------|-----|------|-----|------|

| Line Input to ADC         |         |                      |     |      |     |      |

| Input Signal Level (0dB)  | VINLINE |                      |     | 1AVD |     | VPP  |

|                           |         |                      |     | D    |     |      |

| Signal to Noise Ratio     | SNR     | A-weighted, 0dB gain |     | 86   |     | dB   |

|                           |         | @ fs = 48kHz         |     |      |     |      |

|                           |         |                      |     |      |     |      |

| Dynamic Range             | DR      | A-weighted, -60dB    |     | 86   |     | dB   |

|                           |         | full                 |     |      |     |      |

|                           |         | scale input          |     |      |     |      |

| Total Harmonic Distortion | THD+N   | input, 0dB gain      |     | -71  |     | dB   |

| +Noise Ratio              |         |                      |     |      |     |      |

| Power Supply Rejection    | PSRR    | 1kHz, 50mVpp         |     | -33  |     | dB   |

| Ratio                     |         |                      |     |      |     |      |

| PARAMETER                 | SYMBOL      | TEST<br>CONDITIONS   | MIN | TYP  | MAX | UNIT |

|---------------------------|-------------|----------------------|-----|------|-----|------|

| LINE OUT FROM DAC         |             |                      |     |      |     |      |

| Input Signal Level (0dB)  | VINLINE     |                      |     | 1AVD |     | VPP  |

|                           |             |                      |     | D    |     |      |

| Signal to Noise Ratio     | SNR         | A-weighted, 0dB gain |     | 95   |     | dB   |

|                           | <b>&gt;</b> | @ fs = 48kHz         |     |      |     |      |

| Dynamic Range             | DR          | A-weighted, -60dB    |     | 95   |     | dB   |

|                           |             | full                 |     |      |     |      |

|                           |             | scale input          |     |      |     |      |

| Total Harmonic Distortion | THD+N       | input, 0dB gain      |     | -68  |     | dB   |

| +Noise Ratio              |             |                      |     |      |     |      |

| Power Supply Rejection    | PSRR        | 1kHz, 50mVpp         |     | -33  |     | dB   |

| Ratio                     |             |                      |     |      |     |      |

<u>www.eshine-ic.com</u> 8 / 92 2022.06

#### 5 .Function description

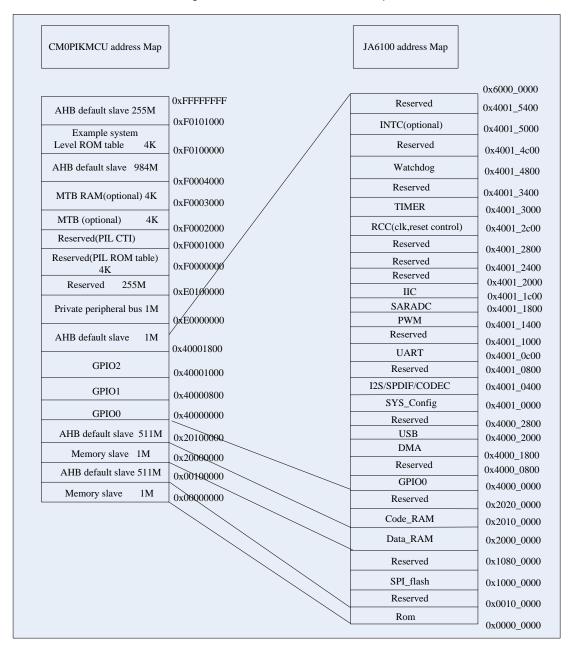

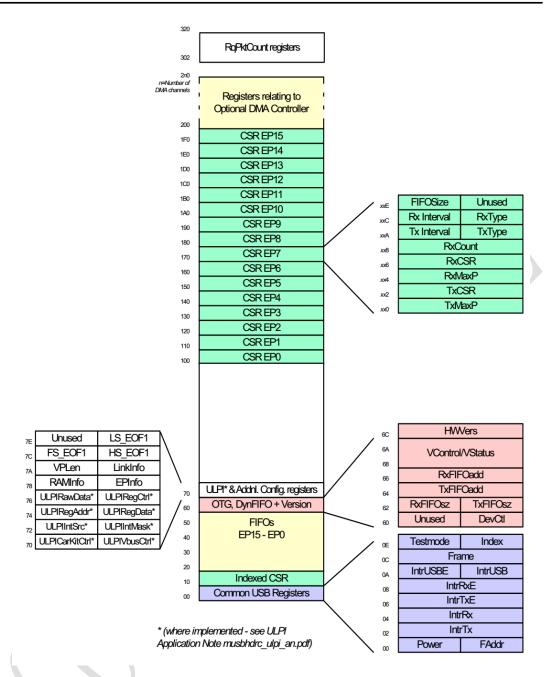

#### 5.1 CJC6822 address map

Figure 3 shows CJC6822 address map.

Figure 3 CJC6822 address map

www.eshine-ic.com 9 / 92 2022.06

#### 5.2 BUS interface unit

CJC6822 chip integrate 2 AHB bus and 1 APB (AMBA protocol compatible). CPU core operates as AHB master in one AHB bus, and DMA controller operates as AHB master on other AHB bus. One AHB2APB Bridge is used for peripherals configuration.(see Figure 1).

#### **5.3 ROM**

CJC6822 integrate 1KB boot ROM. When ISP is available, CPU Boots from internal boot ROM, Receives program code from UART bus and Stores in external flash. If normal mode is enabled, CPU Boots from internal boot ROM, Fetch program code from external SPI flash and Stores in internal SRAM, then, re-mapping memory configuration, boots from internal SRAM.

#### **5.4 SRAM**

The embedded high-speed SRAM is designed for both program code and scratchpad RAM. CJC6822 integrates one 16KB SRAM as the system program memory, 16KB SRAM as the data memory.

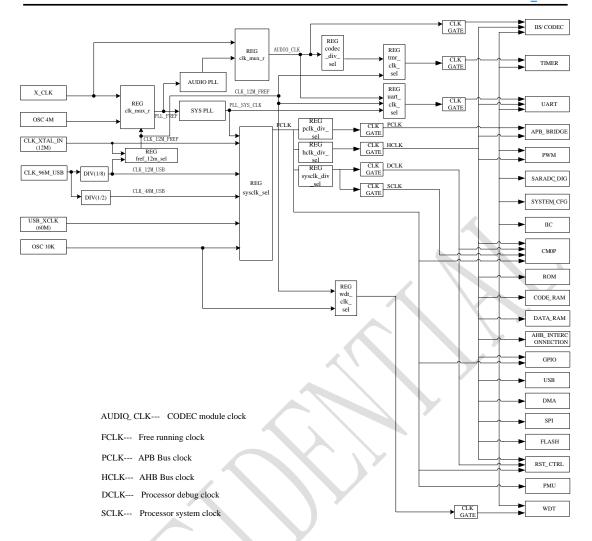

#### 5.5 PLL and clock generation

PLL module generates system and block level clock from the 12MHz USB-oscillator or an external 12MHz crystal. CJC6822 chip contains two clock domains: one is system PLL clock source domain and another is Audio processor clock source domain. System PLL clock source domain includes CPU clock, AHB clock, APB clock based on the 12MHz clock source; Audio processor clock source domain offer clock source for audio processor according to the audio sampling rate, if sampling rate is 8KHz, 16KHz, 32KHz, 48KHz and so on, the APU clock is 24.576MHz and if sampling rate is 22KHz, 44.1KHz and so on, the APU clock is 22.5792MHz. The APU PLL output can be configured via registers.

CJC6822 chip has one internal low-power oscillator to generate 10KHz output. Figure 4 is CJC6822 clock diagram.

www.eshine-ic.com 10 / 92 2022.06

Figure 4 CJC6822 clock diagram

Table 2 system control register list (BaseAddr = 0x4001\_0000).

| Addr. | Name | Туре | Default | Bit     | Default                                       |

|-------|------|------|---------|---------|-----------------------------------------------|

| 0x00  | R0   | R/W  | 0x0     | [31:16] | Reserved                                      |

|       |      |      |         | [15:14] | mux_ctrl_gpio7: 2'h1:GPIO7, 2'h0: UART_RXD    |

|       |      |      |         | [13:12] | mux_ctrl_gpio6: 2'h1: GPIO6, 2'h2: UART_TXD   |

|       |      |      |         | [11:10] | mux_ctrl_gpio5: 2'h1:GPIO5                    |

|       |      |      |         | [9:8]   | mux_ctrl_gpio4: 2'h1:GPIO4                    |

|       |      |      |         | [7:6]   | mux_ctrl_gpio3: 2'h1:GPIO3                    |

|       |      |      |         | [5:4]   | mux_ctrl_gpio2: 2'h1:GPIO2                    |

|       |      |      |         | [3:2]   | mux_ctrl_gpio1: 2'h1: GPIO1                   |

|       |      |      |         | [1:0]   | mux_ctrl_gpio0: 2'h1: GPIO0, 2'h2: PWM output |

| 0x04  | R1   | R/W  | 0x0     | [31:1]  | Reserved                                      |

|       |      |      |         | [0]     | sys_remap : 1:enable & reset                  |

|       |      |      |         |         | 1: Address 32'h0000_0000 remap to code_ram    |

|       |      |      |         |         | 0: Address 32'h0000_0000 remap to ROM         |

| 0x08  | R2   | R/W  | 0x0     | [31:9]  | Reserved                                      |

|       |      |      |         | [8]     | PLL 12MHz reference clock source select:      |

<u>www.eshine-ic.com</u> 11 / 92 2022.06

|   |   |       | CJC6822A_V1.2                                     |

|---|---|-------|---------------------------------------------------|

|   |   |       | clk_xtal_in: 12MHz clock from IO PAD CLK_XTAL     |

|   |   |       | clk_12m_usb: 12MHz clock from USB_oscillator      |

|   |   |       | fref_12m_sel:                                     |

|   |   |       | 1,clk_12m_fref = clk_xtal_in;                     |

|   |   |       | 0,clk_12m_fref = clk_12m_usb                      |

|   |   | [7:4] | A clock mux for PLL reference clock select, audio |

|   |   |       | clock source select and X_CLK PAD clock out       |

|   |   |       | source select.                                    |

|   |   |       | clk_4m: 4MHz clock from RC_oscillator             |

|   |   |       | clk_12m_fref: 12MHz clock for reference           |

|   |   |       | clk_i: clock input from IO PAD X_CLK              |

|   |   |       | pll_audio_clk_i: audio clock from PLL             |

|   |   |       | pll_sys_clk: system clock from PLL                |

|   |   |       | osc_10k: 10kHz clock from internal oscillator     |

|   |   |       | clk_o: clock output from IO PAD X_CLK             |

|   |   |       |                                                   |

|   |   |       | clk_mux:                                          |

|   |   |       | b0000: pll_fref = clk_4m;                         |

|   |   |       | pll_audio_clk_w = pll_audio_clk_i;                |

|   |   |       | $clk_o = 1'h0;$                                   |

|   |   |       | b0001: pll_fref = clk_12m_fref;                   |

|   |   |       | pll_audio_clk_w = clk_i;                          |

|   |   |       | clk_o = 1'h0;                                     |

|   |   |       | b0010: pll_fref = clk_i;                          |

|   |   |       | pll_audio_clk_w = pll_audio_clk_i;                |

|   |   |       | clk_o = 1'h0;                                     |

|   |   |       | b1000: pll_fref = clk_12m_fref;                   |

|   |   |       | pll_audio_clk_w = pll_audio_clk_i;                |

|   |   |       | clk_o = pll_sys_clk;                              |

|   |   |       | b1001: pll_fref = clk_12m_fref;                   |

|   |   |       | pll_audio_clk_w = pll_audio_clk_i;                |

|   | 7 |       | clk_o = pll_audio_clk_i;                          |

|   |   |       | b1010: pll_fref = clk_12m_fref;                   |

| 1 |   |       | pll_audio_clk_w = pll_audio_clk_i;                |

|   |   |       | clk_o = osc_10k;                                  |

|   |   |       | b1011: pll_fref = clk_12m_fref;                   |

|   |   |       | pll_audio_clk_w = pll_audio_clk_i;                |

|   |   |       | clk_o = clk_12m_fref;                             |

|   |   |       | other: pll_fref = clk_12m_fref;                   |

|   |   |       | pll_audio_clk_w = pll_audio_clk_i;                |

|   |   |       | clk_o = 1'h0;                                     |

|   |   | [3]   | pll_bypass                                        |

|   |   |       | 1: Bypass PLL, sys_clk/audio_clk = fref_clk       |

|   |   | [2:1] | lvr_in:                                           |

|   | 1 |       |                                                   |

| Config the threshold voltage for low voltage reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b01 : 2.4V   b10 : 2.7V   b11 : 3V   [0]                       0x0C   R3   R/W   0x0   [31:4]                 [3]                           [4]                       [5]                     [6]                     [7]                   [7]               [8]                 [9]                   [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]               [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                   [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]               [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                 [9]                   [9]                   [9]                   [9]                   [9]                   [9]                     [9]                     [9]                     [9]                     [9]                     [9]                       [9]                         [9]                         [9]                             [9]                             [9]                               [9]                                     [9] |

| b10 : 2.7V     b11 : 3V     [0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| b11 : 3V   [0]   Ivr_en : enable low voltage reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0C         R3         R/W         0x0         [31:4]         Reserved           [3]         Sys_pll_rstn: Sys clock PLL reset         1:reset           0: work         [2]         Audio_pll_rstn: audio pll reset           1: reset         0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| [3] Sys_pll_rstn: Sys clock PLL reset  1:reset  0: work  [2] Audio_pll_rstn: audio pll reset  1: reset  0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1:reset 0: work  [2] Audio_pll_rstn: audio pll reset 1: reset 0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0: work  [2] Audio_pll_rstn: audio pll reset 1: reset 0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [2] Audio_pll_rstn: audio pll reset 1: reset 0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1: reset<br>0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| [1] Sys nll ndn: Sys clock PLL nower down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1:power down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [0] Audio_pll_pdn: audio pll power down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1:power down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0: work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x10 R4 R/W 0x0 [31:24] Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [23:22] codec_div_sel: pll_audio_clk_w divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0: pll_audio_clk_div = pll_audio_clk_w/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1: pll_audio_clk_div = pll_audio_clk_w/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2: pll_audio_clk_div = pll_audio_clk_w/8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Others: pll_audio_clk_div = pll_audio_clk_w/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [21:16] tmr_clk_sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [17:16] == 'h0: tmr1_clk_w=clk_12m_fref                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [17:16] == 'h1: tmr1_clk_w=pll_audio_clk_div                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |