# **CJC8972**

Stereo CODEC and 3W Audio Power Amplifier for

**Portable Audio Applications**

| Edition | Author | Date   | Description                                                                  |

|---------|--------|--------|------------------------------------------------------------------------------|

| V1.0    | By TF  | 2018.9 | Stereo CODEC and 3W Audio Power Amplifier for Portable<br>Audio Applications |

### **DESCRIPTION**

The CJC8972 is a low power, high quality stereo CODEC designed for portable digital audio applications and a mono bridged audio power amplifier capable of delivering 3W of continuous average power into a 3  $\Omega$  load with less than 10% THD when powered by a 5V power supply.

The device integrates complete interfaces to ONE stereo headphone or line out ports. External component requirements are drastically reduced as no separate headphone amplifiers are required. Advanced on-chip digital signal processing performs graphic equalizer, 3-D sound enhancement and automatic level control for the microphone or line input. The CJC8972 can operate as a master or a slave, with various master clock frequencies including 12 or 24MHz for USB devices, or standard 256fs rates like 12.288MHz and 24.576MHz. Different audio sample rates such as 96 kHz, 48 kHz, 44.1 kHz are generated directly from the master clock without the need for an external PLL.

To conserve power in portable applications, the CJC8972 power shutdown mode (IQ = $0.6\,\mu\text{A}$ , typ) is activated when VDD is applied to the SHUTDOWN pin. Boomer audio power amplifiers are designed specifically to provide high power, high fidelity audio output. They require few external components and operate on low supply voltages from 2.0V to 5.5V. Since the CJC8972 does not require output coupling capacitors, bootstrap capacitors, or snubbed networks, it is ideally suited for low-power portable systems that require minimum volume and weight.

The CJC8972 operates at supply voltages down to 1.8V, although the digital core can operate at voltages down to 1.5V to save power, and the maximum for all supplies is 3Volts. Different sections of the chip can also be powered down under software control. The CJC8972 is supplied in a very small and thin 4x4mm COL package, ideal for use in hand-held and portable systems.

www.eshine-ic.com 2 12/4/2018

### **FEATURES**

- DAC SNR 91dB ('A' weighted), THD -81.2dB at 48kHz, 1.8V

- ADC SNR 92.7dB ('A' weighted), THD -82dB at 48kHz, 1.8V

- Programmable ALC / Noise Gate

- 2x On-chip Headphone Drivers

- -THD -74.5dB, SNR 91dB with  $16\Omega$  load Hz, 1.8V

- Digital Graphic Equalizer

- Low Power

- -7mW stereo playback (1.8V supplies)

- -13mW record and playback (1.8V supplies)

- Low Supply Voltages

- -Analogue 1.8V to 3V

- -Digital core: 1.5V to 3V

- -Digital I/O: 1.8V to 3V

- 256fs / 384fs or USB master clock rates: 12MHz, 24MHz

- Audio sample rates: 8, 11.025, 16, 22.05, 24, 32, 44.1, 48,

- 88.2, 96kHz generated internally from master clock

- PO at 10% THD+N, 1kHz

- LD:  $3\Omega$ ,  $4\Omega$  loads 3W (typ), 2.5W (typ)

- All other packages:  $8\Omega$  load 1.5W (typ)

- Shutdown current 0.6 µA (typ)

- Supply voltage range 2.0V to 5.5V

- THD at 1kHz at 1W continuous average output power

- into  $8\Omega$  0.5% (max)

- 4x4mm COL package

### **APPLICATIONS**

- Portable Multimedia players

- Multimedia handsets

- Handheld gaming

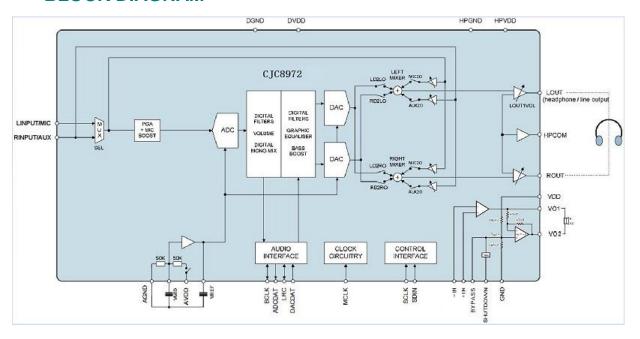

# **BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| DESCRIPTION                            | 2  |

|----------------------------------------|----|

| FEATURES                               | 3  |

| APPLICATIONS                           | 3  |

| TABLE OF CONTENTS                      | 5  |

| PIN CONFIGURATION AND DEVICE MARKING   | 7  |

| PIN DESCRIPTION                        | 8  |

| ABSOLUTE MAXIMUM RATINGS               | 9  |

| RECOMMENDED OPERATION CONDITIONS       | 9  |

| ELECTRICAL CHARACTERISTICS             | 10 |

| NORMAL MODE                            | 10 |

| HPCOM MODE                             | 13 |

| POWER CONSUMPTION                      | 15 |

| Amplifier ELECTRICAL CHARACTERISTICS   | 16 |

| SIGNAL TIMING REQUIREMENTS             | 17 |

| SYSTEM CLOCK TIMING                    | 17 |

| AUDIO INTERFACE TIMING – MASTER MODE   | 18 |

| AUDIO INTERFACE TIMING – SLAVE MODE    | 19 |

| CONTROL INTERFACE TIMING – 2-WIRE MODE | 20 |

| NTERNAL POWER ON RESET CIRCUIT         | 21 |

| DEVICE DESCRIPTION                     | 23 |

| INTRODUCTION                           | 23 |

| INPUT SIGNAL PATH                      | 24 |

| SIGNAL INPUTS                          | 24 |

| PGA CONTROL                            | 25 |

| ANALOGUE TO DIGITAL CONVERTER (ADC)    | 26 |

| ADC DIGITAL FILTER                     | 26 |

| DIGITAL ADC VOLUME CONTROL             | 27 |

| AUTOMATIC LEVEL CONTROL (ALC)          | 28 |

| PEAK LIMITER                           | 31 |

| NOISE GATE                             | 32 |

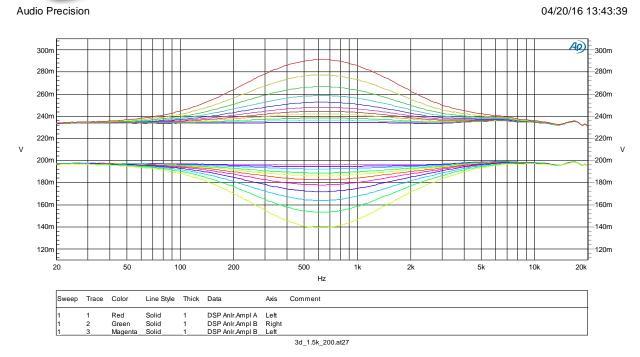

| 3D STEREO ENHANCEMENT                  | 33 |

| OUTPUT SIGNAL PATH                     | 34 |

| DIGITAL DAC VOLUME CONTROL             | 35 |

| GRAPHIC EQUALISER                      | 36 |

| DIGITAL TO ANALOGUE CONVERTER (DAC)    | 37 |

| OUTPUT MIXERS                          | 38 |

| ANALOGUE OUTPUTS                       | 40 |

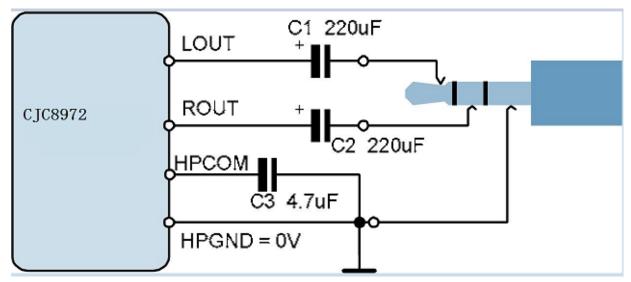

| LOUT/ROUT COMMON GROUND Enable (HPCOM) | 41 |

| ENABLING THE OUTPUTS                   | 42 |

| THERMAL SHUTDOWN                       | 42 |

| DIGITAL AUDIO INTERFACE                | 43 |

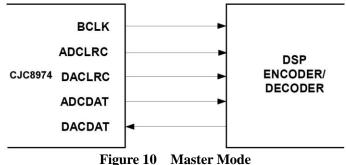

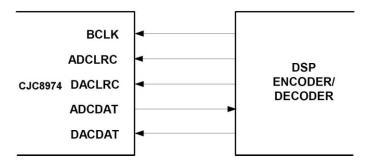

| MASTER AND SLAVE MODE OPERATION              | 43 |

|----------------------------------------------|----|

| AUDIO DATA FORMATS                           | 44 |

| AUDIO INTERFACE CONTROL                      | 47 |

| AUDIO INTERFACE OUTPUT TRISTATE              | 48 |

| MASTER MODE LRC ENABLE                       | 48 |

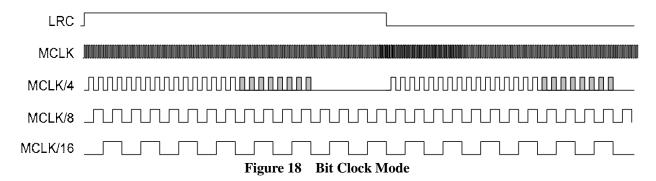

| BIT CLOCK MODE                               | 49 |

| CLOCKING AND SAMPLE RATES                    | 50 |

| CONTROL INTERFACE                            | 53 |

| POWER SUPPLIES                               | 54 |

| POWER MANAGEMENT                             | 55 |

| STOPPING THE MASTER CLOCK                    | 56 |

| SAVING POWER BY REDUCING BIAS CURRENTS       | 57 |

| SAVING POWER BY REDUCING OVERSAMPLING RATE   | 57 |

| SAVING POWER AT HIGHER SUPPLY VOLTAGES       | 58 |

| Device shutdown mode                         | 58 |

| REGISTER MAP                                 | 59 |

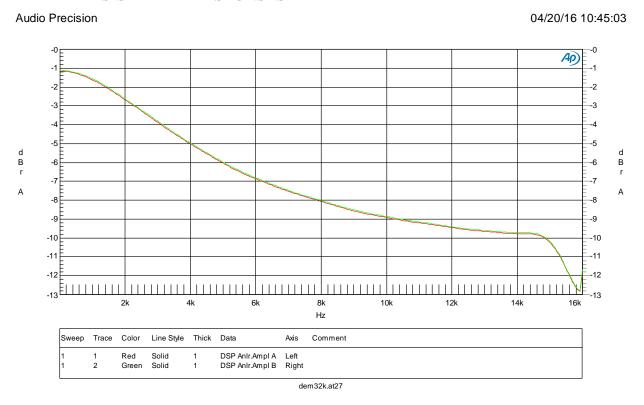

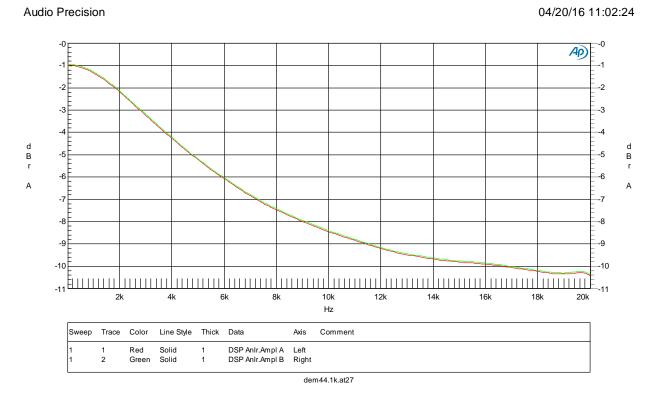

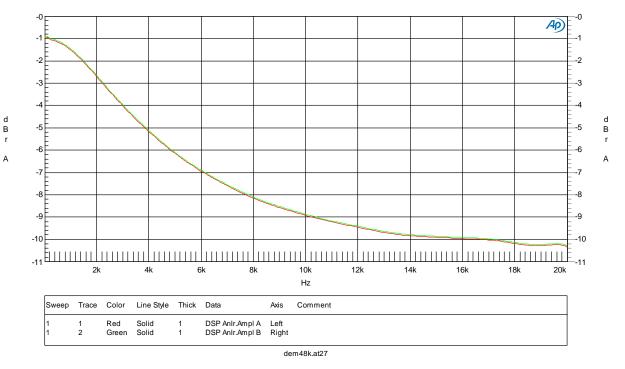

| DIGITAL FILTER CHARACTERISTICS               | 61 |

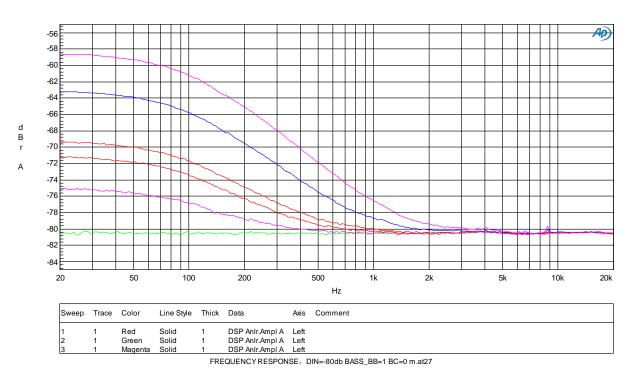

| DAC FILTER RESPONSES                         | 62 |

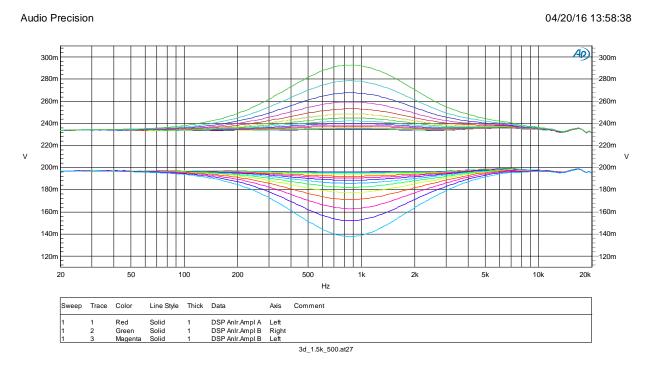

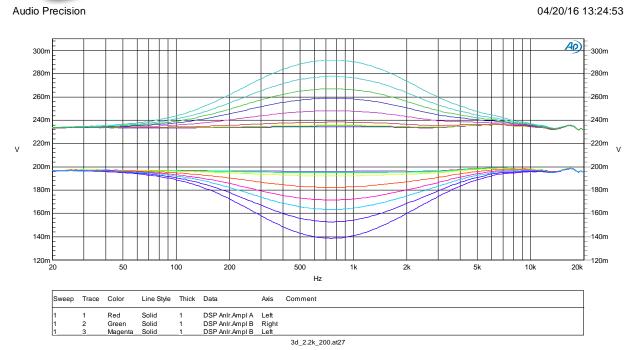

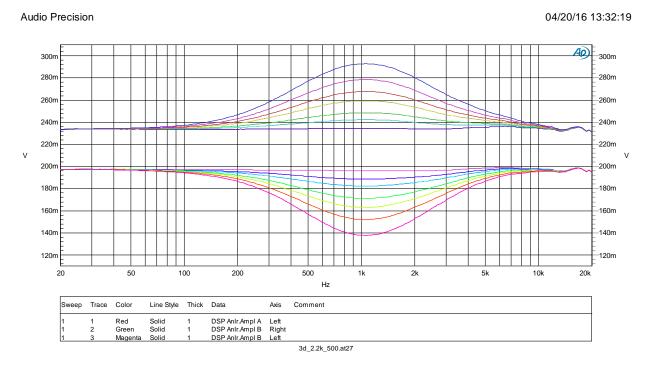

| 3D STEREO ENHANCEMENT                        | 63 |

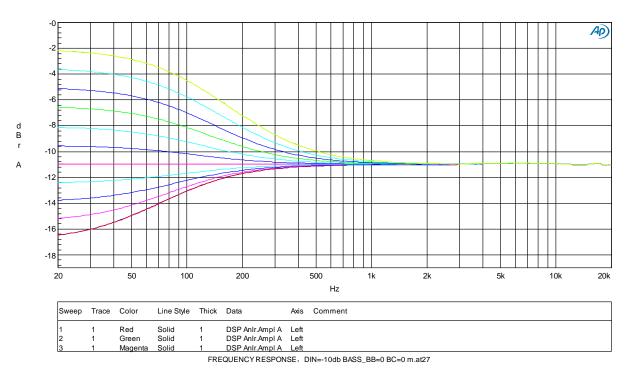

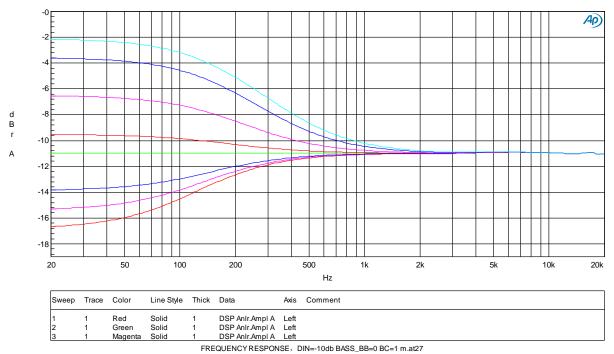

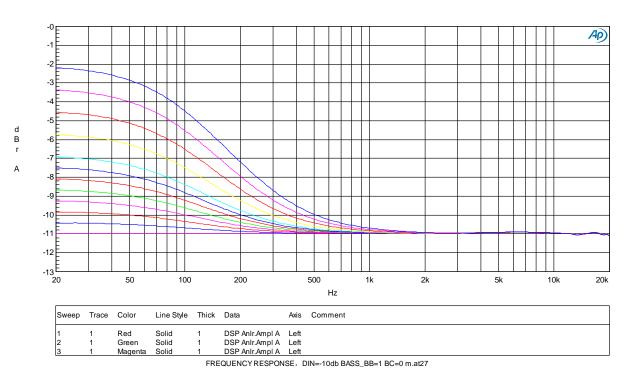

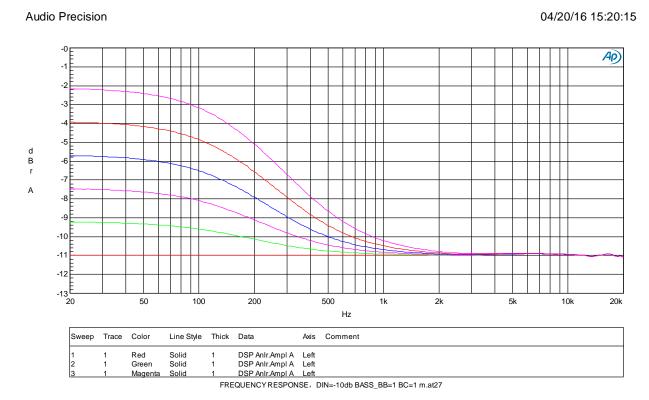

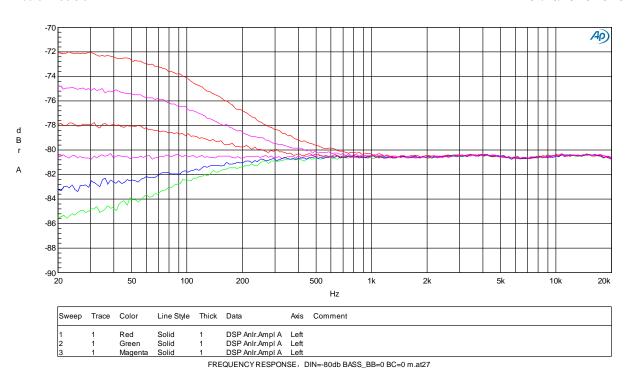

| BASS BOOST FUNCTION                          | 66 |

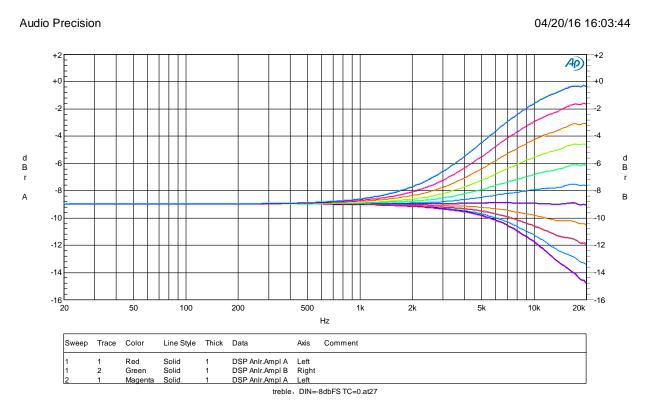

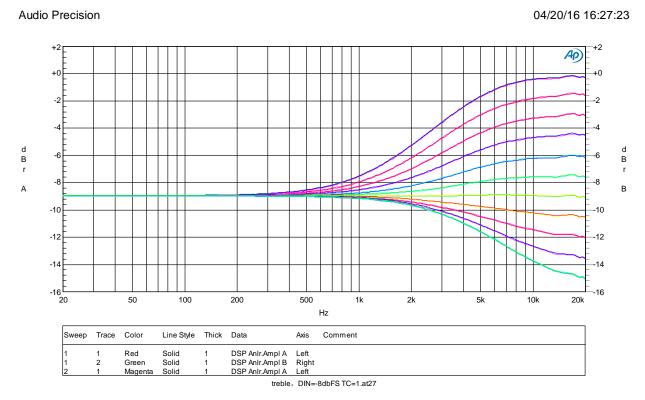

| Treble Filter Characteristic                 | 70 |

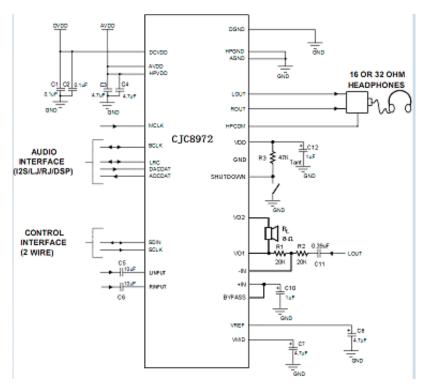

| APPLICATIONS INFORMATION                     | 71 |

| RECOMMENDED EXTERNAL COMPONENTS              |    |

| LINE INPUT CONFIGURATION                     | 71 |

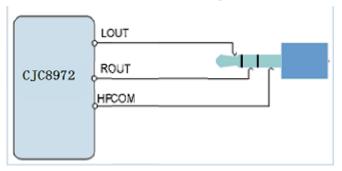

| HEADPHONE OUTPUT CONFIGURATION               | 72 |

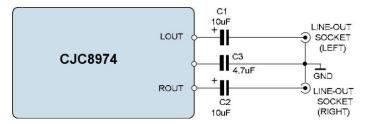

| LINE OUTPUT CONFIGURATION                    | 73 |

| BRIDGE CONFIGURATION EXPLANATION             | 74 |

| MINIMISING POP NOISE AT THE ANALOGUE OUTPUTS | 74 |

| POWER MANAGEMENT EXAMPLES                    | 75 |

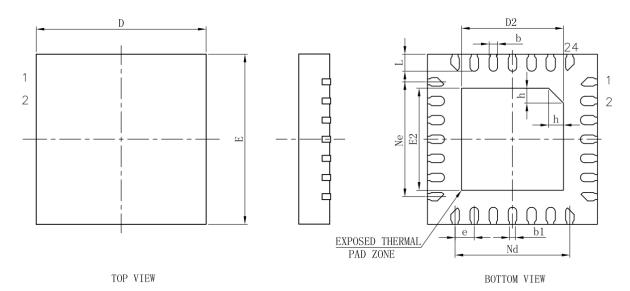

| PACKAGE DIMENSIONS                           | 76 |

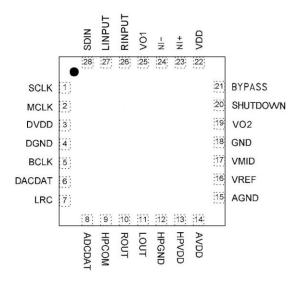

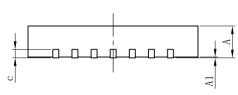

# PIN CONFIGURATION AND DEVICE MARKING

# **PIN DESCRIPTION**

| PIN | NAME     | TYPE   | DESCRIPTION                                                   |

|-----|----------|--------|---------------------------------------------------------------|

| NO  |          |        |                                                               |

| 1   | SCLK     | I      | Control Interface Clock Input                                 |

| 2   | MCLK     | I      | Master Clock                                                  |

| 3   | DVDD     | Supply | Digital Core Supply AND I/O Supply                            |

| 4   | DGND     | Supply | Digital Ground                                                |

| 5   | BCLK     | I/O    | Audio Interface Bit Clock                                     |

| 6   | DACDAT   | I      | DAC Digital Audio Data                                        |

| 7   | LRC      | I/O    | Audio Interface Left / Right Clock                            |

| 8   | ADCDAT   | 0      | ADC Digital Audio Data                                        |

| 9   | HPCOM    | I      | LOUT and ROUT common mode output                              |

| 10  | ROUT     | 0      | Right Output (Line or Headphone)                              |

| 11  | LOUT     | 0      | Left Output (Line or Headphone)                               |

| 12  | HPGND    | Supply | Supply for Analogue Output Drivers (LOUT1/2, ROUT1/2)         |

| 13  | HPVDD    | Supply | Supply for Analogue Output Drivers (LOUT1/2, ROUT1/2, MONOUT) |

| 14  | AVDD     | Supply | Analogue Supply                                               |

| 15  | AGND     | Supply | Analogue Ground (return path for AVDD)                        |

| 16  | VREF     | 0      | Reference Voltage Decoupling Capacitor                        |

| 17  | VMID     | 0      | Midrail Voltage Decoupling Capacitor                          |

| 18  | GND      | Supply | Analogue Ground                                               |

| 19  | VO2      | О      | VO2 Output                                                    |

| 20  | SHUTDOWN | I      | Shutdown Control 1=off, 0=on                                  |

| 21  | BYPASS   | I      | Voltage Reference                                             |

| 22  | VDD      | Supply | Analogue Supply                                               |

| 23  | +IN      | I      | Audio amplifier input +                                       |

| 24  | -IN      | I      | Audio amplifier input -                                       |

| 25  | VO1      | О      | VO1 Output                                                    |

| 26  | RINPUT   | I      | Right Channel Input                                           |

| 27  | LINPUT   | I      | Left Channel Input                                            |

| 28  | SDIN     | I/O    | Control Interface Data Input / 2-wire Acknowledge output      |

### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuous operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically to damage from excessive static voltages. Proper ESD precautions must be taken during handling of this device.

China Semiconductor tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable conditions prior to surface mount assembly. These levels are:

**MSL1** = unlimited floor life at  $<30 \,\mathrm{C} / 85\%$  Relative Humidity. Not normally stored in moisture barrier bag.

**MSL2** = out of bag storage for 1 year at  $<30 \, \text{C} / 60\%$  Relative Humidity. Supplied in moisture barrier bag.

**MSL3** = out of bag storage for 168 hours at <30  $^{\circ}$ C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                           | MIN        | MAX        |

|-------------------------------------|------------|------------|

| Supply voltages                     | -0.3V      | +3.6V      |

| Voltage range digital inputs        | DGND -0.3V | DVDD +0.3V |

| Voltage range analogue inputs       | AGND -0.3V | AVDD +0.3V |

| Operating temperature range, TA     | -25 ℃      | +85 ℃      |

| Storage temperature after soldering | -65 ℃      | +150 ℃     |

#### **Notes:**

- 1. Analogue and digital grounds must always be within 0.3V of each other.

- 2. All digital and analogue supplies are completely independent from each other.

### RECOMMENDED OPERATION CONDITIONS

| PARAMETER                          | SYMBOL           | MIN | TYP | MAX | UNIT |

|------------------------------------|------------------|-----|-----|-----|------|

| Digital supply range (Core/Buffer) | DVDD             | 1.8 |     | 3   | V    |

| Analogue supplies range            | AVDD, HPVDD      | 1.8 |     | 3   | V    |

| Ground                             | DGND,AGND, HPGND |     | 0   |     | V    |

www.eshine-ic.com 9 12/4/2018

# **ELECTRICAL CHARACTERISTICS**

# **NORMAL MODE**

# **Test Conditions**

DVDD = AVDD = HPVDD = 1.8V, TA = +25 °C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                             | SYMBOL      | TEST CONDITIONS                 | MIN   | TYP   | MAX   | UNIT |

|---------------------------------------|-------------|---------------------------------|-------|-------|-------|------|

| Analogue Inputs (LINPUT1,             | RINPUT1, L  | INPUT2, RINPUT2) to AD          | C out |       |       |      |

| Full Scale Input Signal               | VINFS       | AVDD = 2.4V                     | 0.690 | 0.727 | 0.763 | Vrms |

| Level (for ADC 0dB Input at 0dB Gain) |             | <b>AVDD</b> = 1.8V              | 0.480 | 0.545 | 0.610 |      |

| Input Resistance                      | MIC         | MIC to ADC, PGA gain = 0dB      | 16    | 22    |       | kΩ   |

|                                       |             | MIC to ADC,<br>PGA gain = +30dB | 1.5   | 2.8   |       |      |

| Input Capacitance                     |             |                                 |       | 10    |       | pF   |

| Signal to Noise Ratio                 | SNR         | AVDD = 2.4V                     |       | 94    |       | dB   |

| (A-weighted)                          |             | AVDD = 1.8V                     |       | 92    |       |      |

| Total Harmonic Distortion<br>+ Noise  | THD+N       | -6dBr input,<br>AVDD = 2.4V     |       | -86   |       | ID.  |

|                                       |             | -2dBr input,<br>AVDD = 1.8V     |       | -82   |       | dB   |

| Analogue Outputs (LOUT1/2             | 2, ROUT1/2) |                                 |       |       |       |      |

| 0dB Full scale output                 | VOUTFS      | <b>AVDD</b> = <b>2.4V</b>       | 0.690 | 0.727 | 0.763 | Vrms |

| voltage                               |             | AVDD = 1.8V                     | 0.507 | 0.545 | 0.583 |      |

| Signal to Noise Ratio                 | SNR         | AVDD = 2.4V                     |       | 96    |       | dB   |

| (A-weighted)                          |             | <b>AVDD</b> = <b>1.8V</b>       |       | 93    |       | ав   |

| Total Harmonic Distortion + Noise     | THD+N       | -0dBr input,<br>AVDD = 2.4V     |       | 80    |       |      |

|                                       |             | -4dBr input,<br>AVDD = 2.4V     |       | 87    |       | 150  |

|                                       |             | -0dBr input,<br>AVDD = 1.8V     |       | 80    |       | dB   |

|                                       |             | -6dBr input,<br>AVDD = 1.8V     |       | 84    |       |      |

# **Test Conditions**

$DVDD = AVDD = HPVDD = 1.8V \quad , \ TA = +25 \ ^{\circ}C, \ 1kHz \ signal, \ fs = 48kHz, \ PGA \ gain = 0dB, \ 24-bit \ audio \ data \ unless \ otherwise \ stated.$

| PARAMETER          | SYMBOL      | TEST CONDITIONS   | MIN       | TYP        | MAX      | UNIT |

|--------------------|-------------|-------------------|-----------|------------|----------|------|

| Headphone Outp     | ut (LOUT1/R | OUT1, LOUT2/ROUT2 | AC couple | d to load) |          |      |

| Total Harmonic     | THD+N       | HPVDD=2.4V,       |           | 74         |          | dB   |

| Distortion +       |             | RL=16Ω PO=5mW     |           |            |          |      |

| Noise              |             | HPCOM=LCOM=1      |           |            |          |      |

|                    |             | HPVDD=1.8V,       |           | 74         |          | dB   |

|                    |             | RL=16Ω PO=5mW     |           |            |          |      |

|                    |             | HPCOM=LCOM=0      |           |            |          |      |

| Signal to Noise    | SNR         | HPVDD=2.4V,       |           | 94         |          | dB   |

| Ratio              |             | HPCOM=LCOM=1      |           |            |          |      |

| (A-weighted)       |             | HPVDD=1.8V,       |           | 91         |          | dB   |

|                    |             | HPCOM=LCOM=0      |           |            |          |      |

| Analogue Referen   | nce Levels  |                   |           |            |          |      |

| Midrail            | VMID        |                   | -3%       | AVDD/2     | +3%      | V    |

| Reference          |             |                   |           |            |          |      |

| Voltage            |             |                   |           |            |          |      |

| Buffered           | VREF        |                   | -3%       | AVDD/2     | +3%      | V    |

| Reference          |             |                   |           |            |          |      |

| Voltage            |             |                   |           |            |          |      |

| Digital Input / Or | utput       |                   |           |            |          |      |

| Input HIGH         | VIH         |                   | 0.7×DB    |            |          | V    |

| Level              |             |                   | VDD       |            |          |      |

| Input LOW          | VIL         |                   |           |            | 0.3×DVDD | V    |

| Level              |             |                   |           |            |          |      |

| <b>Output HIGH</b> | VOH         | IOH = +1mA        | 0.9×DB    |            |          | V    |

| Level              |             |                   | VDD       |            |          |      |

| Output LOW         | VOL         | IOL = -1mA        |           |            | 0.1×DVDD | V    |

| Level              |             |                   |           |            |          |      |

# **Test Conditions**

DVDD = AVDD = HPVDD = 1.8V, TA =  $+25\,^{\circ}$ C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                           | SYMBOL | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |

|-----------------------------------------------------|--------|-----------------|-----|-----|-----|------|--|

| DAC to Line-Out (L/ROUT1 or L/ROUT2 with 10kΩ load) |        |                 |     |     |     |      |  |

| Signal to Noise Ratio                               | SNR    | AVDD = 2.4V     |     | 93  |     | dB   |  |

| (A-weighted)                                        |        | HPCOM=LCOM=1    |     |     |     |      |  |

|                                                     |        | AVDD=1.8V       |     | 91  |     |      |  |

|                                                     |        | HPCOM=LCOM=0    |     |     |     |      |  |

| Total Harmonic                                      | THD+N  | AVDD = 2.4V     |     | 76  |     | dB   |  |

| Distortion + Noise                                  |        | HPCOM=LCOM=1    |     |     |     |      |  |

|                                                     |        | AVDD=1.8V       |     | 81  |     |      |  |

|                                                     |        | HPCOM=LCOM=0    |     |     |     |      |  |

| <b>Channel Separation</b>                           |        | min             |     | 101 |     | dB   |  |

|                                                     |        | 1kHz signal     |     | 111 |     |      |  |

# **HPCOM MODE**

## **Test Conditions**

$DVDD = AVDD = HPVDD = 1.8V \ , \ TA = +25 \, ^{\circ}\!\! C \ , \ 1kHz \ signal, \ fs = 48kHz, \ PGA \ gain = 0dB, \ 24-bit \ audio \ data \ unless \ otherwise \ stated.$

| PARAMETER                             | SYMBOL      | TEST CONDITIONS                                               | MIN   | TYP   | MAX   | UNIT |

|---------------------------------------|-------------|---------------------------------------------------------------|-------|-------|-------|------|

| Analogue Inputs (LINPUT1,             | RINPUT1, L  | INPUT2, RINPUT2) to AD                                        | C out |       |       |      |

| Full Scale Input Signal               | VINFS       | AVDD = 2.4V                                                   | 0.690 | 0.727 | 0.763 | Vrms |

| Level (for ADC 0dB Input at 0dB Gain) |             | AVDD = 1.8V                                                   | 0.480 | 0.545 | 0.610 |      |

| Input Resistance                      | MIC         | MIC to ADC, PGA gain = 0dB                                    | 16    | 22    |       | kΩ   |

|                                       |             | MIC to ADC,<br>PGA gain = +30dB                               | 1.5   | 2.8   |       |      |

| Input Capacitance                     |             |                                                               |       | 10    |       | pF   |

| Signal to Noise Ratio                 | SNR         | AVDD = 2.4V                                                   |       | 97    |       | dB   |

| (A-weighted)                          |             | AVDD = 1.8V                                                   |       | 94    |       |      |

| Total Harmonic Distortion + Noise     | THD+N       | -6dBr input,<br>AVDD = 2.4V                                   |       | -86   |       | 15   |

|                                       |             | -2dBr input,<br>AVDD = 1.8V                                   |       | -82   |       | dB   |

| Analogue Outputs (LOUT1/2             | 2, ROUT1/2) |                                                               |       |       |       |      |

| 0dB Full scale output                 | VOUTFS      | AVDD = 2.4V                                                   | 0.690 | 0.727 | 0.763 | Vrms |

| voltage                               |             | AVDD = 1.8V                                                   | 0.507 | 0.545 | 0.583 |      |

| Signal to Noise Ratio (A-weighted)    | SNR         | AVDD = $2.4V$<br>RL= $16 \Omega$ PO= $5mW$<br>HPCOM=LCOM= $1$ |       | 92    |       | ID.  |

|                                       |             | AVDD = 1.8V<br>RL=16 $\Omega$ PO=5mW<br>HPCOM=LCOM=1          |       | 91    |       | dB   |

| Total Harmonic Distortion + Noise     | THD+N       | -1dBr input, AVDD = 2.4V RL=16 Ω PO=5mW HPCOM=LCOM=1          |       | 76    |       | 10   |

|                                       |             | -2dBr input, AVDD = 1.8V RL=16Ω PO=5mW HPCOM=LCOM=1           |       | 72    |       | dB   |

# **Test Conditions**

$DVDD = AVDD = HPVDD = 1.8V \quad , \ TA = +25 \ ^{\circ}C, \ 1kHz \ signal, \ fs = 48kHz, \ PGA \ gain = 0dB, \ 24-bit \ audio \ data \ unless \ otherwise \ stated.$

| PARAMETER         | SYMBOL      | TEST CONDITIONS   | MIN       | TYP        | MAX      | UNIT |

|-------------------|-------------|-------------------|-----------|------------|----------|------|

| Headphone Outp    | ut (LOUT1/R | OUT1, LOUT2/ROUT2 | AC couple | d to load) |          |      |

| Total Harmonic    | THD+N       | HPVDD=2.4V,       |           | 71         |          | dB   |

| Distortion +      |             | RL=16Ω PO=5mW     |           |            |          |      |

| Noise             |             | HPCOM=LCOM=1      |           |            |          |      |

|                   |             |                   |           |            |          |      |

|                   |             | HPVDD=1.8V,       |           | 71         |          | dB   |

|                   |             | RL=16Ω PO=5mW     |           |            |          |      |

|                   |             | HPCOM=LCOM=0      |           |            |          |      |

| Signal to Noise   | SNR         | HPVDD=2.4V,       |           | 92         |          | dB   |

| Ratio             |             | HPCOM=LCOM=1      |           |            |          |      |

| (A-weighted)      |             |                   |           |            |          |      |

| ,                 |             | HPVDD=1.8V,       |           | 92         |          | dB   |

|                   |             | HPCOM=LCOM=0      |           |            |          |      |

|                   |             | DACMIXBIAS=0      |           |            |          |      |

| Analogue Referen  | nce Levels  |                   |           |            |          |      |

| Midrail           | VMID        |                   | -3%       | AVDD/2     | +3%      | V    |

| Reference         |             |                   |           |            |          |      |

| Voltage           |             |                   |           |            |          |      |

| Buffered          | VREF        |                   | -3%       | AVDD/2     | +3%      | V    |

| Reference         |             |                   |           |            |          |      |

| Voltage           |             |                   |           |            |          |      |

| Digital Input / O | utput       |                   |           |            |          |      |

| Input HIGH        | VIH         |                   | 0.7×DB    |            |          | V    |

| Level             |             |                   | VDD       |            |          |      |

| Input LOW         | VIL         |                   |           |            | 0.3×DVDD | V    |

| Level             |             |                   |           |            |          |      |

| Output HIGH       | VOH         | IOH = +1mA        | 0.9×DB    |            |          | V    |

| Level             |             |                   | VDD       |            |          |      |

| Output LOW        | VOL         | IOL = -1mA        |           |            | 0.1×DVDD | V    |

| Level             |             |                   |           |            |          |      |

## **POWER CONSUMPTION**

The power consumption of the CJC8972 depends on the following factors.

- Supply voltages: Reducing the supply voltages also reduces supply currents, and therefore results in significant power savings, especially in the digital sections of the CJC8972.

- Operating mode: Significant power savings can be achieved by always disabling parts of the CJC8972 that are not used (e.g. mic pre-amps, unused outputs, DAC, ADC, etc.)

| AVDD=HPVI | DD=DVDD =1.8V AIN=NONE DIN  | =NONE |      |       |      |          |

|-----------|-----------------------------|-------|------|-------|------|----------|

|           |                             |       |      |       |      |          |

| MODE      |                             | DVDD  | AVDD | HPVDD | SUM  | UNIT     |

|           | ADC                         | 0.713 | 2.65 | 0     | 3.36 |          |

|           | DAC LINEOUT                 | 1.447 | 2.34 | 0.197 | 3.98 | <b>A</b> |

| NORMAL    | DAC HEADPHONE( $16\Omega$ ) | 1.36  | 2.34 | 0.215 | 3.92 | mA       |

| NORWAL    | BYPASS                      | 0.294 | 1.92 | 0.328 | 2.54 |          |

|           | POWER DOWN                  | 0.9   | 0.1  | 0.1   | 1.1  | uA       |

|           |                             |       |      |       |      |          |

|           | ADC                         | 0.73  | 2.66 | 0.036 | 3.43 |          |

|           | DAC HEADPHONE( $16\Omega$ ) | 1.044 | 2.36 | 4.48  | 7.88 |          |

| прсом     | DAC HEADPHONE(32Ω)          | 1.044 | 2.36 | 4.46  | 7.86 | mA       |

| HPCOM     | BYPASS(16Ω)                 | 0.289 | 1.85 | 4.58  | 6.72 |          |

|           | BYPASS(32Ω)                 | 0.289 | 1.85 | 4.57  | 6.71 |          |

|           | POWER DOWN                  | 0.9   | 0.1  | 0.1   | 1.1  | uA       |

### **Notes:**

- 1. All figures are at TA = +25 °C, Slave Mode, fs = 48kHz, MCLK = 12.288 MHz (256fs),

- 2. The power dissipated in the headphone is not included in the above table.

# Amplifier electrical characteristics

The following specifications apply for VDD = 5V and RL =  $8\Omega$  unless otherwise specified. Limits apply for TA =  $25^{\circ}$ C.

| Symbol | Parameter                         | Conditions                                  |     | am   | plifier |       |

|--------|-----------------------------------|---------------------------------------------|-----|------|---------|-------|

|        |                                   |                                             | Min | Тур  | Limit   | Units |

| VDD    | Supply Voltage                    |                                             | 2.0 |      | 5.5     | V     |

| IDD    | Quiescent Power Supply<br>Current | VIN = 0V, $Io = 0A$                         |     | 6.5  | 10.0    | mA    |

| ISD    | Shutdown Current                  | VPIN1 = VDD                                 |     | 0.6  | 2       | uA    |

| VOS    | Output Offset Voltage             | VIN = 0V                                    |     | 5.0  | 50      | mV    |

| Po     | Output Power                      | THD = $1\%$ , $f = 1kHz$                    |     |      |         | W     |

|        |                                   | $R_L = 4\Omega$                             |     | 2    |         |       |

|        |                                   | $R_L = 8\Omega$                             |     | 1.2  |         |       |

|        |                                   | THD = $1\%$ , $f = 1kHz$                    |     |      |         | W     |

|        |                                   | $R_L = 4\Omega$                             |     | 2.5  |         |       |

|        |                                   | $R_{L}=8\Omega$                             |     | 1.5  |         |       |

| THD+   | Total Harmonic                    | $20$ Hz $\leq$ f $\leq$ $20$ kHz, AVD = $2$ |     |      |         | %     |

| N      | Distortion+Noise                  | $R_L = 4\Omega$ , $P_O = 1.6W$              |     | 0.13 |         |       |

|        |                                   | $R_L = 8\Omega$ , $P_O = 1W$                |     | 0.25 |         |       |

| PSRR   | Power Supply Rejection            | VDD = 4.9V  to  5.1V                        |     | 60   |         | DB    |

|        | Ratio                             |                                             |     |      |         |       |

# **SIGNAL TIMING REQUIREMENTS**

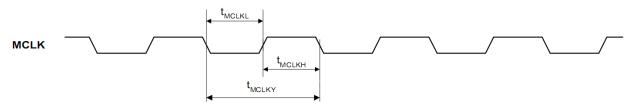

### **SYSTEM CLOCK TIMING**

**Figure 1 System Clock Timing Requirements**

### **Test Conditions**

CLKDIV2=0, DVDD = 1.8V, DGND = 0V, TA =  $+25^{\circ}$ C, Slave Mode fs = 48kHz, MCLK = 384fs, 24-bit data, unless otherwise stated.

| PARAMETER                              | SYMBOL  | MIN   | TYP | MAX   | UNIT |

|----------------------------------------|---------|-------|-----|-------|------|

| <b>System Clock Timing Information</b> |         |       |     |       |      |

| MCLK System clock pulse width high     | TMCLKL  | 21    |     |       | ns   |

| MCLK System clock pulse width low      | Тмськн  | 21    |     |       | ns   |

| MCLK System clock cycle time           | TMCLKY  | 54    |     |       | ns   |

| MCLK duty cycle                        | TMCLKDS | 60:40 |     | 40:60 | ns   |

#### **Test Conditions**

CLKDIV2=1, DVDD = 1.8V, DGND = 0V, TA = +25 C, Slave Mode fs = 48kHz, MCLK = 384fs, 24-bit data, unless otherwise stated.

| PARAMETER                          | SYMBOL | MIN | TYP | MAX | UNIT |

|------------------------------------|--------|-----|-----|-----|------|

| System Clock Timing Information    |        |     |     |     |      |

| MCLK System clock pulse width high | TMCLKL | 10  |     |     | ns   |

| MCLK System clock pulse width low  | Тмськн | 10  |     |     | ns   |

| MCLK System clock cycle time       | TMCLKY | 27  |     |     | ns   |

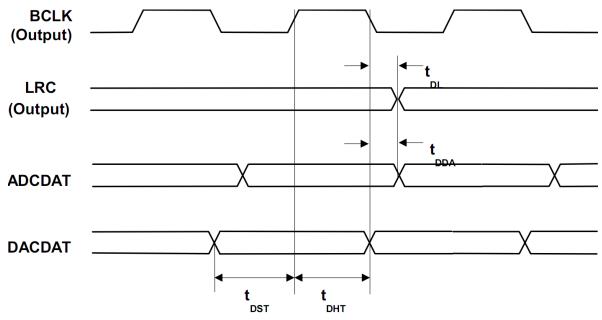

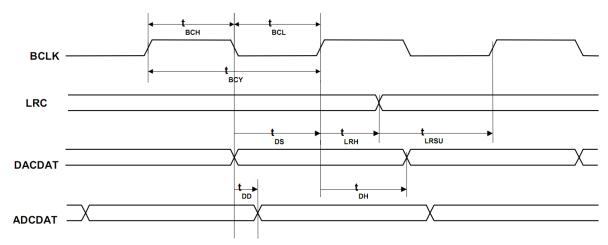

# **AUDIO INTERFACE TIMING - MASTER MODE**

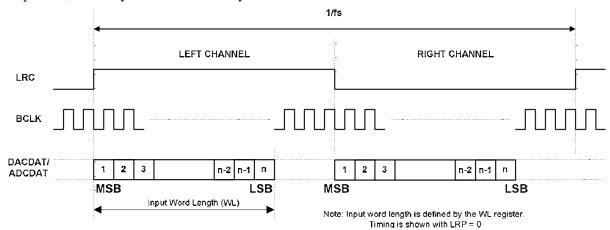

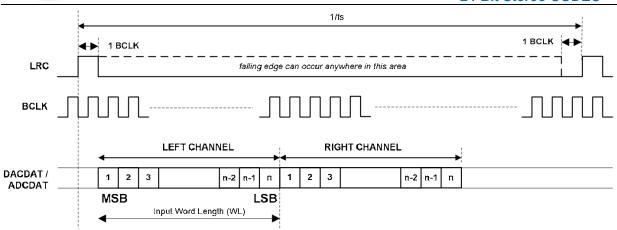

Figure 2 Digital Audio Data Timing – Master Mode

### **Test Conditions**

DVDD = 1.8V, DGND = 0V, TA = +25 C, Slave Mode, fs = 48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                             | SYMBOL  | MIN | TYP     | MAX | UNIT |

|---------------------------------------|---------|-----|---------|-----|------|

| Bit Clock Timing Information          |         |     |         |     |      |

| BCLK rise time (10pF load)            | tBCLKR  |     |         | 3   | ns   |

| BCLK fall time (10pF load)            | tBCLKF  |     |         | 3   | ns   |

| BCLK duty cycle (normal mode, BCLK =  | tBCLKDS |     | 50:50   |     |      |

| MCLK/n)                               |         |     |         |     |      |

| BCLK duty cycle (USB mode, BCLK =     | tBCLKDS |     | Tmclkds |     |      |

| MCLK)                                 |         |     |         |     |      |

| Audio Data Input Timing Information   |         |     |         |     |      |

| DACLRC propagation delay from BCLK    | tDL     |     |         | 10  | ns   |

| falling edge                          |         |     |         |     |      |

| ADCDAT propagation delay from BCLK    | tDDA    |     |         | 10  | ns   |

| falling edge                          |         |     |         |     |      |

| DACDAT setup time to BCLK rising edge | tDST    | 10  |         |     | ns   |

| DACDAT hold time from BCLK rising     | tDHT    | 10  |         |     | ns   |

| edge                                  |         |     |         |     |      |

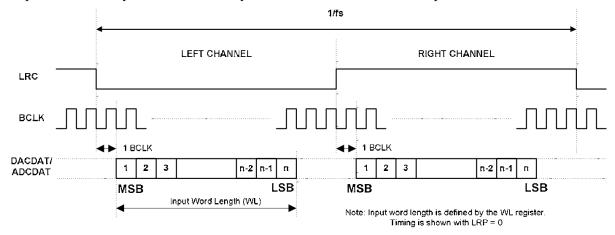

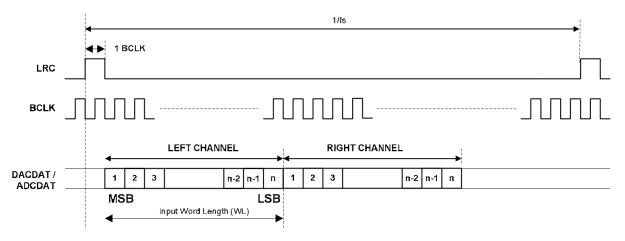

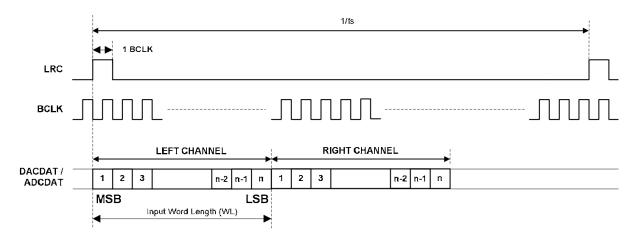

# **AUDIO INTERFACE TIMING - SLAVE MODE**

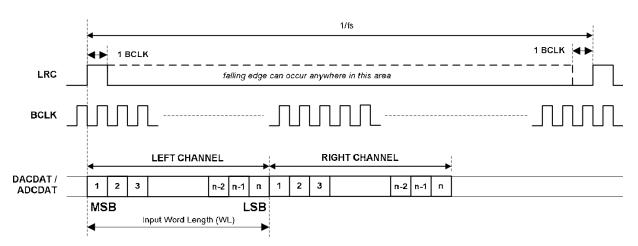

Figure 3 Digital Audio Data Timing – Slave Mode

#### **Test Conditions**

DVDD = 1.8V, DGND = 0V, TA = +25 C, Slave Mode, fs = 48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                  | SYMBOL | MIN | TYP | MAX | UNIT |  |  |  |

|--------------------------------------------|--------|-----|-----|-----|------|--|--|--|

| Audio Data Input Timing Information        |        |     |     |     |      |  |  |  |

| BCLK cycle time                            | tBCY   | 50  |     |     | ns   |  |  |  |

| BCLK pulse width high                      | tBCH   | 20  |     |     | ns   |  |  |  |

| BCLK pulse width low                       | tBCL   | 20  |     |     | ns   |  |  |  |

| DACLRC set-up time to BCLK rising edge     | tLRSU  | 10  |     |     | ns   |  |  |  |

| DACLRC hold time from BCLK rising edge     | tLRH   | 10  |     |     | ns   |  |  |  |

| DACDAT hold time from BCLK rising edge     | tDH    | 10  |     |     | ns   |  |  |  |

| ADCDAT propagation delay from BCLK falling | tDD    |     |     | 10  | ns   |  |  |  |

| edge                                       |        |     |     |     |      |  |  |  |

#### Note:

BCLK period should always be greater than or equal to MCLK period.

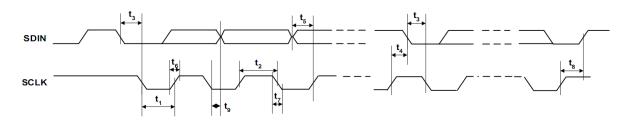

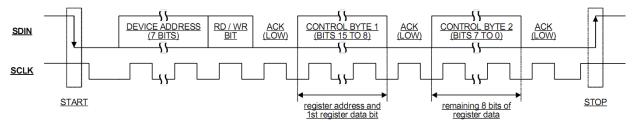

# **CONTROL INTERFACE TIMING – 2-WIRE MODE**

Figure 5 Control Interface Timing – 2-Wire Serial Control Mode

### **Test Conditions**

DVDD = 1.8V,DGND = 0V, TA = +25 C, Slave Mode, fs = 48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| otherwise stated.                             |        |     |     |     |      |

|-----------------------------------------------|--------|-----|-----|-----|------|

| PARAMETER                                     | SYMBOL | MIN | TYP | MAX | UNIT |

| Program Register Input Information            |        |     |     |     |      |

| SCLK Frequency                                |        | 0   |     | 526 | KHZ  |

| SCLK Low Pulse-Width                          | t1     | 1.3 |     |     | us   |

| SCLK High Pulse-Width                         | t2     | 600 |     |     | ns   |

| <b>Hold Time (Start Condition)</b>            | t3     | 600 |     |     | ns   |

| <b>Setup Time (Start Condition)</b>           | t4     | 600 |     |     | ns   |

| <b>Data Setup Time</b>                        | t5     | 100 |     |     | ns   |

| SDIN, SCLK Rise Time                          | t6     |     |     | 300 | ns   |

| SDIN, SCLK Fall Time                          | t7     |     |     | 300 | ns   |

| <b>Setup Time (Stop Condition)</b>            | t8     | 600 |     |     | ns   |

| Data Hold Time                                | t9     |     |     | 900 | ns   |

| Pulse width of spikes that will be suppressed | tps    | 0   |     | 5   | ns   |

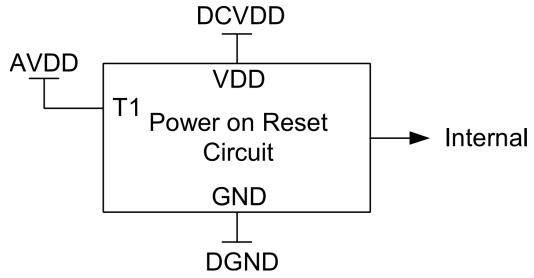

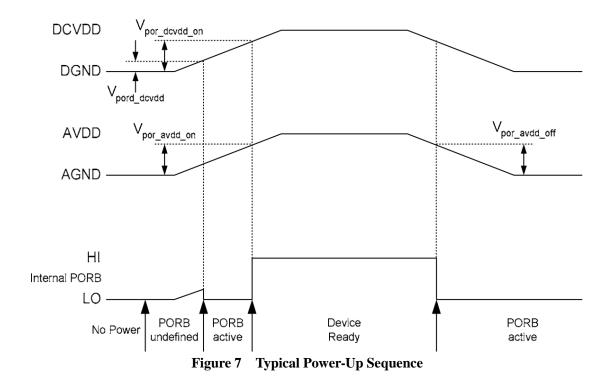

### INTERNAL POWER ON RESET CIRCUIT

Figure 6 Internal Power on Reset Circuit Schematic

The CJC8972 includes an internal Power-On-Reset Circuit, as shown in Figure 6, which is used to reset the digital logic into a default state after power up. The power on reset circuit is powered from DVDD and monitors DVDD and AVDD. It asserts PORB low if DVDD or AVDD are below a minimum threshold.

Figure 7 shows a typical power-up sequence. When DVDD and AVDD rise above the minimum thresholds, Vpord\_dvdd and Vpord\_avdd, there is enough voltage for the circuit to guarantee the Power on Reset is asserted low and the chip is held in reset. In this condition, all writes to the control interface are ignored. When DVDD rises to Vpor\_dvdd\_on and AVDD rises to Vpor\_avdd\_on, PORB is released high and all registers are in their default state and writes to the control interface may take place. If DVDD and AVDD rise at different rates then PORB will only be released when DVDD and AVDD have both exceeded the Vpor\_dvdd\_on and Vpor\_avdd\_on thresholds.

On power down, PORB is asserted low whenever DVDD drops below the minimum threshold Vpor\_dvdd\_off or AVDD drops below the minimum threshold Vpor\_avdd\_off.

| SYMBOL        | MIN | TYP  | MAX | UNIT |

|---------------|-----|------|-----|------|

| Vpord_dvdd    | 0.4 | 0.6  | 0.8 | V    |

| Vpor_dvdd_on  | 0.9 | 1.26 | 1.6 | V    |

| Vpor_avdd_on  | 0.5 | 0.7  | 0.9 | V    |

| Vpor_avdd_off | 0.4 | 0.6  | 0.8 | V    |

Table 3 Typical POR Operation (typical values, not tested)

### **DEVICE DESCRIPTION**

#### INTRODUCTION

The CJC8972 is a low power audio codec offering a combination of high quality audio, advanced features, low power and small size. These characteristics make it ideal for portable digital audio applications such as MP3 and minidisk player / recorders. Stereo 24-bit multi-bit delta sigma ADCs and DACs are used with oversampling digital interpolation and decimation filters.

The device includes TWO analogue inputs that as MIC input, that is MICINP and MICINN. As the MIC phone is single end mode we can use MICINP as input PIN. If the MIC phone is differential then MICINP and MICINN should be use. A programmable gain amplifier with automatic level control (ALC) keeps the recording volume constant. The on-chip stereo ADC and DAC are of a high quality using a multi-bit, low-order oversampling architecture to deliver optimum performance with low power consumption.

The DAC output signal first enters an analogue mixer where an analogue input and/or the post-ALC signal can be added to it. This mix is available on line and headphone outputs.

The CJC8972 has a configurable digital audio interface where ADC data can be read and digital audio playback data fed to the DAC. It supports a number of audio data formats including I2 S, DSP Mode (a burst mode in which frame sync plus 2 data packed words are transmitted), MSB-First, left justified and can operate in master or slave modes.

The CJC8972 uses a unique clocking scheme that can generate many commonly used audio sample rates from either a 12.00MHz USB clock or an industry standard 256/384 fs clock. This feature eliminates the common requirement for an external phase-locked loop (PLL) in applications where the master clock is not an integer multiple of the sample rate. Sample rates of 8kHz, 11.025kHz, 12kHz, 16kHz, 22.05kHz, 24kHz, 32kHz, 44.1kHz, 48kHz, 88.2kHz and 96kHz can be generated.

The digital filters used for recording and playback are optimized for each sampling rate used.

The design of the CJC8972 has given much attention to power consumption without compromising performance. It operates at very low voltages, and includes the ability to power off parts of the circuitry under software control, including standby and power off modes.

#### **INPUT SIGNAL PATH**

The input signal path consists of a MIC inputs, followed by a PGA (programmable gain amplifier) and an optional microphone gain boost.. The gain of the PGA can be controlled either by the user or by the on-chip ALC function (see Automatic Level Control).

The signal then enters an ADC where it is digitized.

### **SIGNAL INPUTS**

The CJC8972 has two high independence, low capacitance AC coupled analogue inputs, MICINP / MICINN. Inputs can be configured as microphone or line level by enabling or disabling the microphone gain boost.

MIC\_DIF\_EN control bits (see Table 4) are used to select independently between single-ended input and internally generated differential products (MICINP-MICINN). The choice of differential signal OR single-ended input, MICINP-MICINN or MICINP, which is chosen using MIC\_DIF\_EN (refer to Table 6).

The CJC8972 can be set up to convert differential or one single ended mono signal by applying the differential signal to MICINP/MICINN or the single ended signal MICINP. For example, by setting MIC\_DIF\_EN to high, the differential signal (MICINP-MICINN) go to PGA path.

The signal inputs are biased internally to the reference voltage VREF. Whenever the line inputs are muted or the device placed into standby mode, the inputs are kept biased to VREF using special anti-thump circuitry. This reduces any audible clicks that may otherwise be heard when changing inputs.

| REGISTER     | BIT | LABEL      | DEFAULT | DESCRIPTION                                  |

|--------------|-----|------------|---------|----------------------------------------------|

| ADDRESS      |     |            |         |                                              |

| R32 (20h)    | 8   | MIC_DIF_EN | 0       | 0: MICINP single-ended input into ADC        |

| ADC Signal   |     |            |         | 1: MICINP and MICINN differential input into |

| Path Control |     |            |         | ADC                                          |

|              | 5:4 | MIC BOOST  | 00      | Microphone Gain Boost                        |

|              |     |            |         | 00 = Boost off (bypassed)                    |

|              |     |            |         | 01 = 13dB boost                              |

|              |     |            |         | 10 = 20dB boost                              |

|              |     |            |         | 11 = 29dB boost                              |

#### Table 4 MIC input control and gain adjust

#### **PGA CONTROL**

The PGA matches the input signal level to the ADC input range. The PGA gain is logarithmically adjustable from +30dB to -17.25dB in 0.75dB steps. Each PGA can be controlled either by the user or by the ALC function (see Automatic Level Control). When ALC is enabled for one or both channels, then writing to the corresponding PGA control register has no effect.

The gain is independently adjustable on both Right and Left Line Inputs. Additionally, by controlling the register bits LIVU and RIVU, the left and right gain settings can be simultaneously updated. Setting the LZCEN and RZCEN bits enables a zero-cross detector which ensures that PGA gain changes only occur when the signal is at zero, eliminating any zipper noise. If zero cross is enabled a timeout is also available to update the gain if a zero cross does not occur. This function may be enabled by setting TOEN in register R23 (17h).

The inputs can also be muted in the analogue domain under software control. The software control registers are shown in Table 9.If zero crossing is enabled, it is necessary to enable zero cross timeout to un-mute the input PGAs. This is because their outputs will not cross zero when muted. Alternatively, zero cross can be disabled before sending the un-mute command.

| REGISTER | BIT | LABEL   | DEFAULT | DESCRIPTION                                     |

|----------|-----|---------|---------|-------------------------------------------------|

| ADDRESS  |     |         |         |                                                 |

| R0 (00h) | 8   | LIVU    | 0       | Volume Update                                   |

| Channel  |     |         |         | 0 = Store LINVOL in intermediate latch (no gain |

| PGA      |     |         |         | change)                                         |

|          |     |         |         | 1 = Update left and right channel gains (left = |

|          |     |         |         | LINVOL, right = intermediate latch)             |

|          | 7   | LINMUTE | 1       | Channel Input Analogue Mute                     |

|          |     |         |         | 1 = Enable Mute                                 |

|          |     |         |         | 0 = Disable Mute                                |

|          |     |         |         | Note: LIVU must be set to un-mute.              |

|          | 6   | LZCEN   | 0       | Channel Zero Cross Detector                     |

|          |     |         |         | 1 = Change gain on zero cross only              |

|          |     |         |         | 0 = Change gain immediately                     |

|          | 5:0 | LINVOL  | 010111  | Channel Input Volume Control                    |

|          |     | [5:0]   | (0dB)   | 1111111 = +30dB                                 |

|          |     |         |         | 1111110 = +29.25 dB                             |

|          |     |         |         | 0.75dB steps down to                            |

|          |     |         |         | 000000 = -17.25dB                               |

| R23 (17h)   | 0 | TOEN | 0 | Timeout Enable       |

|-------------|---|------|---|----------------------|

| Additional  |   |      |   | 0 : Timeout Disabled |

| Control (1) |   |      |   | 1 : Timeout Enabled  |

**Table 9 Input PGA Software Control**

### **ANALOGUE TO DIGITAL CONVERTER (ADC)**

The CJC8972 uses a multi-bit, oversampled sigma-delta ADC for each channel. The use of multi-bit feedback and high oversampling rates reduces the effects of jitter and high frequency noise. The ADC Full Scale input level is proportional to AVDD. With a 1.8V supply voltage, the full scale level is 1.0 Volts r.m.s. Any voltage greater than full scale may overload the ADC and cause distortion.

#### **ADC DIGITAL FILTER**

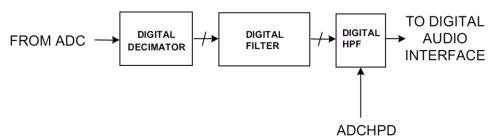

The ADC filters perform true 24 bit signal processing to convert the raw multi-bit oversampled data from the ADC to the correct sampling frequency to be output on the digital audio interface. The digital filter path is illustrated in Figure 8.

Figure 8 ADC Digital Filter

The ADC digital filters contain a digital high-pass filter, selectable via software control. The high-pass filter response is detailed in the Digital Filter Characteristics section. When the high-pass filter is enabled the DC offset is continuously calculated and subtracted from the input signal. By setting HPOR, the last calculated DC offset value is stored when the high-pass filter is disabled and will continue to be subtracted from the input signal. If the DC offset is changed, the stored and subtracted value will not change unless the high-pass filter is enabled. This feature can be used for calibration purposes. In addition the high-pass filter may be enabled separately on the left and right channels (see Table 11).

The output data format can be programmed by the user to accommodate stereo or monophonic recording on both inputs. The polarity of the output signal can also be changed under software control. The software control is shown in Table 10.

| REGISTER | BIT | LABEL  | DEFAULT | DESCRIPTION                                    |

|----------|-----|--------|---------|------------------------------------------------|

| ADDRESS  |     |        |         |                                                |

| R5 (05h) | 5   | ADCPOL | 00      | 0 = Polarity not inverted                      |

| ADC and  |     |        |         | 1 = Polarity invert                            |

| DAC      | 4   | HPOR   | 0       | Store dc offset when high-pass filter disabled |

| Control  |     |        |         | 1 = store offset                               |

|   |        |   | 0 = clear offset                           |

|---|--------|---|--------------------------------------------|

| 0 | ADCHPD | 0 | ADCHPD determine high-pass filter behavior |

|   |        |   | 1 = HPF on                                 |

|   |        |   | 0 = HPF off                                |

**Table 10 ADC Signal Path Control**

### **DIGITAL ADC VOLUME CONTROL**

The output of the ADCs can be digitally amplified or attenuated over a range from -97dB to +30dB in 0.5dB steps. The volume of each channel can be controlled separately. The gain for a given eight-bit code X is given by:

### $0.5 \times (X-195) \, dB$ for $1 \leq X \leq 255$ ; MUTE for X=0

The LAVU and RAVU control bits control the loading of digital volume control data. When LAVU or RAVU are set to 0, the LADCVOL or RADCVOL control data will be loaded into the respective control register, but will not actually change the digital gain setting. Both left and right gain settings are updated when either LAVU or RAVU are set to 1. This makes it possible to update the gain of both channels simultaneously.

| REGISTER       | BIT | LABEL   | DEFAULT  | DESCRIPTION                                      |

|----------------|-----|---------|----------|--------------------------------------------------|

| ADDRESS        |     |         |          |                                                  |

| R21 (15h)      | 7:0 | LADCVOL | 11000011 | Left ADC Digital Volume Control                  |

| ADC            |     | [7:0]   | (0dB)    | 0000 0000 = Digital Mute                         |

| Digital Volume |     |         |          | $0000\ 0001 = -97$ dB                            |

|                |     |         |          | $0000\ 0010 = -96.5$ dB                          |

|                |     |         |          | 0.5dB steps up to                                |

|                |     |         |          | 1111 1111 = +30dB                                |

|                | 8   | LAVU    | 0        | Left ADC Volume Update                           |

|                |     |         |          | 0 = Store LADCVOL in intermediate latch (no gain |

|                |     |         |          | change)                                          |

|                |     |         |          | 1 = Update left and right channel gains (left =  |

|                |     |         |          | LADCVOL, right = intermediate latch)             |

| R22 (16h)      | 7:0 |         |          |                                                  |

| Right ADC      | 8   |         |          |                                                  |

| Digital Volume |     |         |          |                                                  |

**Table 12 ADC Digital Volume Control**

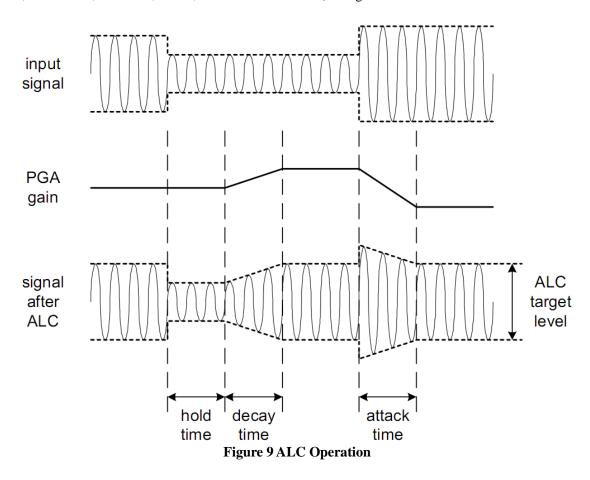

## **AUTOMATIC LEVEL CONTROL (ALC)**

The CJC8972 has an automatic level control that aims to keep a constant recording volume irrespective of the input signal level. This is achieved by continuously adjusting the PGA gain so that the signal level at the ADC input remains constant. A digital peak detector monitors the ADC output and changes the PGA gain if necessary. Note that when the ALC function is enabled, the settings of registers 0 and 1 (LINVOL, LIVU, LIZC, LINMUTE, RINVOL, RIVU, RIZC and RINMUTE) are ignored.

The ALC function is enabled using the ALCSEL control bits. When enabled, the recording volume can be programmed between -6dB and -28.5dB (relative to ADC full scale) using the ALCL register bits. An upper limit for the PGA gain can be imposed by setting the MAXGAIN control bits.

### HLD, DCY and ATK control the hold, decay and attack times, respectively:

Hold time is the time delay between the peak level detected being below target and the PGA gain beginning to ramp up. It can be programmed in power-of-two (2n) steps, e.g. 2.67ms, 5.33ms, 10.67ms etc. up to 43.7s. Alternatively, the hold time can also be set to zero. The hold time only applies to gain ramp-up, there is no delay before ramping the gain down when the signal level is above target.

Decay (Gain Ramp-Up) Time is the time that it takes for the PGA gain to ramp up across 90% of its range (e.g. from –15B up to 27.75dB). The time it takes for the recording level to return to its target value therefore depends on both the decay time and on the gain adjustment required. If the gain adjustment is small, it will be shorter than the decay time. The decay time can be programmed in power-of-two (2) steps, from 24ms, 48ms, 96ms, etc. to 24.58s.

Attack (Gain Ramp-Down) Time is the time that it takes for the PGA gain to ramp down across 90% of its range (e.g. from 27.75dB down to -15B gain). The time it takes for the recording level to return to its target value therefore depends on both the attack time and on the gain adjustment required. If the gain adjustment is small, it will be shorter than the attack time. The attack time can be programmed in power-of-two (2) steps, from 6ms, 12ms, 24ms, etc. to 6.14s.

When operating in stereo, the peak detector takes the maximum of left and right channel peak values, and any new gain setting is applied to both left and right PGAs, so that the stereo image is preserved. However, the ALC function can also be enabled on one channel only. In this case, only one PGA is controlled by the ALC mechanism, while the other channel runs independently with its PGA gain set through the control register.

When one ADC channel is unused or used for DC measurement, the peak detector disregards that channel. The ALC function can also operate when the two ADC outputs are mixed to mono in the digital domain, but not if they are mixed to mono in the analogue domain, before entering the ADCs.

| REGISTER<br>ADDRESS | BI<br>T | LABEL   | DEFAULT          | DESCRIPTION                                     |

|---------------------|---------|---------|------------------|-------------------------------------------------|

| R17 (11h)           | 8       | ALCSEL  | 0                | ALC function select                             |

| ALC Control 1       |         | THEOLE  | (OFF)            | 0 = ALC off (PGA gain set by register)          |

| Tibe condor i       |         |         | (011)            | 1 = Left channel only                           |

|                     |         |         |                  | Note: ensure that LINVOL and RINVOL settings    |

|                     |         |         |                  | (reg. 0) is the same before entering this mode. |

|                     | 6:4     | MAXGAIN | 111              | Set Maximum Gain of PGA                         |

|                     | 0.4     | [2:0]   | (+30dB)          | 111:+30dB                                       |

|                     |         | [2.0]   | (130 <b>dD</b> ) | 110:+24dB                                       |

|                     |         |         |                  | ···.(-6dB steps)                                |

|                     |         |         |                  | .(-oub steps)<br>001 : -6dB                     |

|                     |         |         |                  | 000 : -12dB                                     |

|                     | 2.0     | A L CI  | 1011             |                                                 |

|                     | 3:0     | ALCL    | 1011             | ALC target – sets signal level at ADC Input     |

|                     |         | [3:0]   | (-12dB)          | 0000 = -28.5dB FS                               |

|                     |         |         |                  | 0001 = -27.0dB FS                               |

|                     |         |         |                  | ··· (1.5dB steps)                               |

|                     |         |         |                  | 1110 = -7.5dB FS                                |

|                     |         |         |                  | 1111 = -6dB FS                                  |

| R18 (12h)           | 7       | ALCZC   | 0 (zero cross    | ALC uses zero cross detection circuit.          |

| ALC Control 2       |         |         | off)             |                                                 |

|                     | 3:0     | HLD     | 0000             | ALC hold time before gain is increased.         |

|                     |         | [3:0]   | (0ms)            | 0000 = 0 ms                                     |

|                     |         |         |                  | 0001 = 2.67 ms                                  |

|                     |         |         |                  | 0010 = 5.33ms                                   |

|                     |         |         |                  | ··· (time doubles with every step)              |

|                     |         |         |                  | 1111 = 43.7s                                    |

| R19 (13h)           | 7:4     | DCY     | 0011             | ALC decay (gain ramp-up) time                   |

| ALC Control 3       |         | [3:0]   | (192ms)          | 0000 = 24 ms                                    |

|                     |         |         |                  | 0001 = 48 ms                                    |

|                     |         |         |                  | 0010 = 96 ms                                    |

|                     |         |         |                  | ··· (time doubles with every step)              |

|                     |         |         |                  | 1010 or higher = 24.58s                         |

|                     | 3:0     | ATK     | 0010             | ALC attack (gain ramp-down) time                |

|                     |         | [3:0]   | (24ms)           | 0000 = 6ms                                      |

|                     |         |         |                  | 0001 = 12 ms                                    |

|                     |         |         |                  | 0010 = 24 ms                                    |

|                     |         |         |                  | ··· (time doubles with every step)              |

|                     |         |         |                  | 1010 or higher = 6.14s                          |

#### **Table 13 ALC Control**

### **PEAK LIMITER**

To prevent clipping when a large signal occurs just after a period of quiet, the ALC circuit includes a limiter function. If the ADC input signal exceeds 87.5% of full scale (-1.16dB), the PGA gain is ramped down at the maximum attack rate (as when ATK = 0000), until the signal level falls below 87.5% of full scale. This function is automatically enabled whenever the ALC is enabled.

#### Note:

If ATK = 0000, then the limiter makes no difference to the operation of the ALC. It is designed to prevent clipping when long attack times are used.

#### **NOISE GATE**

When the signal is very quiet and consists mainly of noise, the ALC function may cause "noise pumping", i.e. loud hissing noise during silence periods. The CJC8972 has a noise gate function that prevents noise pumping by comparing the signal level at the LINPUT1/2 and/or RINPUT1/2 pins against a noise gate threshold, NGTH. The noise gate cuts in when:

• Signal level at ADC [dB] < NGTH [dB] + PGA gain [dB] + Mic Boost gain [dB]

### This is equivalent to:

• Signal level at input pin [dB] < NGTH [dB]

The ADC output can then either be muted or alternatively, the PGA gain can be held constant (preventing it from ramping up as it normally would when the signal is quiet).

The table below summarises the noise gate control register. The NGTH control bits set the noise gate threshold with respect to the ADC full-scale range. The threshold is adjusted in 1.5dB steps. Levels at the extremes of the range may cause inappropriate operation, so care should be taken with set—up of the function. Note that the noise gate only works in conjunction with the ALC function, and always operates on the same channel(s) as the ALC (left, right, both, or none).

| REGISTER<br>ADDRESS | BIT | LABEL | DEFAULT | DESCRIPTION                             |

|---------------------|-----|-------|---------|-----------------------------------------|

|                     |     |       | 00000   |                                         |

| R20 (14h)           | 7:3 | NGTH  | 00000   | Noise gate threshold                    |

| Noise Gate          |     | [4:0] |         | 13 -76.5dBfs                            |

| Control             |     |       |         | 13 -75dBfs                              |

|                     |     |       |         | ··· 1.5 dB steps                        |

|                     |     |       |         | 11110 -31.5dBfs                         |

|                     |     |       |         | 11111 -30dBfs                           |

|                     | 2:1 | NGG   | 00      | Noise gate type                         |

|                     |     | [1:0] |         | X0 = PGA gain held constant             |

|                     |     |       |         | 01 = mute ADC output                    |

|                     |     |       |         | 11 = reserved (do not use this setting) |

|                     | 0   | NGAT  | 0       | Noise gate function enable              |

|                     |     |       |         | 1 = enable                              |

|                     |     |       |         | 0 = disable                             |

**Table 14 Noise Gate Control**

#### Note:

The performance of the ADC may degrade at high input signal levels if the monitor bypass mux is selected with MIC boost and ALC enabled.

### **3D STEREO ENHANCEMENT**

The CJC8972 has a digital 3D enhancement option to artificially increase the separation between the left and right channels. This effect can be used for recording or playback, but not for both simultaneously. Selection of 3D for record or playback is controlled by register bit MODE3D.

#### **Important:**

Switching the 3D filter from record to playback or from playback to record may only be done when ADC and DAC are disabled. The CJC8972 control interface will only allow MODE3D to be changed when ADC and DAC are disabled (i.e. bits ADCL, ADCR, DACL and DACR in reg. 26 / 1Ah are all zero).

The 3D enhancement function is activated by the 3DEN bit, and has two programmable parameters. The 3DDEPTH setting controls the degree of stereo expansion. Additionally, one of four filter characteristics can be selected for the 3D processing, using the 3DVC and 3DLC control bits.

| REGISTER<br>ADDRESS | BIT | LABEL   | DEFAULT | DESCRIPTION                        |  |

|---------------------|-----|---------|---------|------------------------------------|--|

| R16 (10h)           | 6   | 3DUC    | 0       | Upper Cut-off frequency            |  |

| 3D enhance          |     |         |         | 0 = High  (2.2kHz at  48kHz)       |  |

|                     |     |         |         | sampling)                          |  |

|                     |     |         |         | 1 = Low (1.5kHz at 48kHz sampling) |  |

|                     | 5   | 3DLC 0  |         | Lower Cut-off frequency            |  |

|                     |     |         |         | 0 = Low (200Hz at 48kHz sampling)  |  |

|                     |     |         |         | 1 = High (500Hz at 48kHz sampling) |  |

|                     | 4:1 | 3DDEPTH | 0000    | Stereo depth                       |  |

|                     |     | [3:0]   |         | 0000: 0% (minimum 3D effect)       |  |

|                     |     |         |         | 0001: 6.67%                        |  |

|                     |     |         |         |                                    |  |

|                     |     |         |         | 1110: 93.3%                        |  |

|                     |     |         |         | 1111: 100% (maximum 3D effect)     |  |

|                     | 0   | 3DEN    | 0       | 3D function enable                 |  |

|                     |     |         |         | 1: enabled                         |  |

|                     |     |         |         | 0: disabled                        |  |

**Table 15 3D Stereo Enhancement Function**

When 3D enhancement is enabled (and/or the graphic equalizer for playback) it may be necessary to attenuate the signal by 6dB to avoid limiting. This is a user selectable function, enabled by setting ADCDIV2 for the record path and DACDIV2 for the playback path.

| REGISTER<br>ADDRESS | BIT | LABEL   | DEFAULT | DESCRIPTION              |  |

|---------------------|-----|---------|---------|--------------------------|--|

| R5 (05h)            | 8   | ADCDIV2 | 0       | ADC 6dB attenuate enable |  |

| ADC and DAC         |     |         |         | 0 = disabled (0dB)       |  |

| control             |     |         |         | 1 = -6dB enabled         |  |

|                     | 7   | DACDIV2 | 0       | DAC 6dB attenuate enable |  |

|                     |     |         |         | 0 = disabled (0dB)       |  |

|                     |     |         |         | 1 = -6dB enabled         |  |

Table 16 ADC and DAC 6dB Attenuation Select

### **OUTPUT SIGNAL PATH**

The CJC8972 output signal paths consist of digital filters, DACs, analogue mixers and output drivers. The digital filters and DACs are enabled when the CJC8972 is in 'playback only' or 'record and playback' mode. The mixers and output drivers can be separately enabled by individual control bits (see Analogue Outputs). Thus it is possible to utilize the analogue mixing and amplification provided by the CJC8972, irrespective of whether the DACs are running or not.

The CJC8972 receives digital input data on the DACDAT pin. The digital filter block processes the data to provide the following functions:

- Digital volume control

- Graphic equalizer and Dynamic Bass Boost

- Sigma-Delta Modulation

Two high performance sigma-delta audio DACs convert the digital data into two analogue signals (left and right). These can then be mixed with analogue signals from the LINPUT1/2 and RINPUT1/2 pins, and the mix is fed to the output drivers, LOUT1/ROUT1 and LOUT2/ROUT2.

• LOUT/ROUT: can drive a  $16\Omega$  or  $32\Omega$  stereo headphone or stereo line output.

### **DIGITAL DAC VOLUME CONTROL**

The signal volume from each DAC can be controlled digitally, in the same way as the ADC volume (see Digital ADC Volume Control). The gain and attenuation range is -127dB to 0dB in 0.5dB steps. The level of attenuation for an eight-bit code X is given by:

$$0.5 \times (X-255) dB$$

for  $1 \le X \le 255$ ; MUTE for  $X = 0$

The LDVU and RDVU control bits control the loading of digital volume control data. When LDVU or RDVU are set to 0, the LDACVOL or RDACVOL control data is loaded into an intermediate register, but the actual gain does not change. Both left and right gain settings are updated simultaneously when either LDVU or RDVU are set to 1.

| REGISTER<br>ADDRESS | BIT | LABEL   | DEFAULT  | DESCRIPTION                             |

|---------------------|-----|---------|----------|-----------------------------------------|

| R10 (0Ah)           | 8   | LDVU    | 0        | Left DAC Volume Update                  |

| Left Channel        |     |         |          | 0 = Store LDACVOL in intermediate       |

| Digital Volume      |     |         |          | latch (no gain change)                  |

|                     |     |         |          | 1 = Update left and right channel       |

|                     |     |         |          | gains (left = LDACVOL, right =          |

|                     |     |         |          | intermediate latch)                     |

|                     | 7:0 | LDACVOL | 11111111 | Left DAC Digital Volume Control         |

|                     |     | [7:0]   | (0dB)    | 0000 0000 = Digital Mute                |

|                     |     |         |          | $0000\ 0001 = -127$ dB                  |

|                     |     |         |          | $0000\ 0010 = -126.5$ dB                |

|                     |     |         |          | 0.5dB steps up to                       |

|                     |     |         |          | 1111 1111 = 0dB                         |

| R11 (0Bh)           | 8   | RDVU    | 0        | Right DAC Volume Update                 |

| Right Channel       |     |         |          | 0 = Store RDACVOL in intermediate       |

| Digital Volume      |     |         |          | latch (no gain change)                  |

|                     |     |         |          | 1 = Update left and right channel       |

|                     |     |         |          | gains (left = intermediate latch, right |

|                     |     |         |          | = RDACVOL)                              |

|                     | 8   | RDVU    | 0        | Right DAC Volume Update                 |

|                     |     |         |          | latch (no gain change)                  |

|                     |     |         |          | 1 = Update left and right channel       |

|                     |     |         |          | gains (left = intermediate latch, right |

|                     |     |         |          | = RDACVOL)                              |

|                     | 7:0 | RDACVOL | 11111111 | Right DAC Digital Volume Control        |

|                     |     | [7:0]   | (0dB)    | similar to LDACVOL                      |

#### **Table 17 Digital Volume Control**

### **GRAPHIC EQUALISER**

The CJC8972 has a digital graphic equalizer and adaptive bass boost function. This function operates on digital audio data before it is passed to the audio DACs. Bass enhancement can take two different forms:

- Linear bass control: bass signals are amplified or attenuated by a user programmable gain.

This is independent of signal volume, and very high bass gains on loud signals may lead to signal clipping.

- Adaptive bass boost: The bass volume is amplified by a variable gain. When the bass volume is low, it is boosted more than when the bass volume is high. This method is recommended because it prevents clipping, and usually sounds more pleasant to the human ear.

Treble control applies a user programmable gain, without any adaptive boost function. Bass and treble control are completely independent with separately programmable gains and filter characteristics.

| REGISTER<br>ADDRESS | BIT | LABEL | DEFAULT    | DESCRIPTION                                        | 4                  |          |  |

|---------------------|-----|-------|------------|----------------------------------------------------|--------------------|----------|--|

| R12 (0Ch)           | 7   | BB    | 0          | Bass Boost                                         |                    |          |  |

| Bass Control        |     |       |            | 0 = Linear bass control<br>1 = Adaptive bass boost |                    |          |  |

|                     |     |       |            |                                                    |                    |          |  |

|                     | 6   | BC    | 11111111   | Bass Filter Characteristic                         |                    |          |  |

|                     |     |       | (0dB)      | 0 = Low Cutoff                                     | (130Hz at 48kHz sa | ampling) |  |

|                     |     |       |            | 1 = High Cutoff                                    | (200Hz at 48kHz s  | ampling) |  |

|                     | 3:0 | BASS  | 1111       | Bass Intensity                                     |                    |          |  |

|                     |     | [3:0] | (Disabled) | Code                                               | BB=0               | BB=1     |  |

|                     |     |       |            | 0000                                               | +9dB               | 15       |  |

|                     |     |       |            | 0001                                               | +9dB               | 14       |  |

|                     |     |       |            | 0010                                               | +7.5dB             | 13       |  |

|                     |     |       |            | 0011                                               | +6dB               | 12       |  |

|                     |     |       |            | 0100                                               | +4.5dB             | 11       |  |

|                     |     |       |            | 0101                                               | +3dB               | 10       |  |

|                     |     |       |            | 0110                                               | +1.5dB             | 9        |  |

|                     |     |       |            | 0111                                               | 0dB                | 8        |  |

|                     |     |       |            | 1000                                               | -1.5dB             | 7        |  |

|                     |     |       |            | 1001                                               | -3dB               | 6        |  |

|                     |     |       |            | 1010                                               | -4.5dB             | 5        |  |

|                     |     |       |            | 1011                                               | -6dB               | 4        |  |

|                     |     |       |            | 1100                                               | -6dB               | 3        |  |

|                |     |       |            | 1101                         | -6dB               | 2       |

|----------------|-----|-------|------------|------------------------------|--------------------|---------|

|                |     |       |            | 1110                         | -6dB               | 1       |

|                |     |       |            | 1111                         | Bypass (OFF)       |         |

| R13 (0Dh)      | 6   | TC    | 0          | Treble Filter Characteristic |                    |         |

| Treble Control |     |       |            | 0 = High Cutoff              | (8kHz at 48kHz sa  | mpling) |

|                |     |       |            | 1 = Low Cutoff               | (4kHz at 48kHz saı | npling) |

|                | 3:0 | TRBL  | 1111       | Treble Intensity             |                    |         |

|                |     | [3:0] | (Disabled) | 0000  or  0001 = +9 dB       |                    |         |

|                |     |       |            | 0010 = +7.5dB                |                    |         |

|                |     |       |            | (1.5dB steps)                | )                  |         |

|                |     |       |            | 1011  to  1110 = -6          | 6dB                |         |

|                |     |       |            | 1111 = Disable               |                    |         |

**Table 18 Graphic Equaliser**

## **DIGITAL TO ANALOGUE CONVERTER (DAC)**

After passing through the graphic equalizer filters, digital 'de-emphasis' can be applied to the audio data if necessary (e.g. when the data comes from a CD with pre-emphasis used in the recording). De-emphasis filtering is available for sample rates of 48kHz, 44.1kHz and 32kHz.